VSC8201 –Я—А–Њ—Б–Љ–Њ—В—А —В–µ—Е–љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Њ–њ–Є—Б–∞–љ–Є—П (PDF) - Vitesse Semiconductor

–Э–Њ–Љ–µ—А –≤ –Ї–∞—В–∞–ї–Њ–≥–µ

–Ъ–Њ–Љ–њ–Њ–љ–µ–љ—В—Л –Ю–њ–Є—Б–∞–љ–Є–µ

–њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М

VSC8201

VSC8201 Datasheet PDF : 21 Pages

| |||

VSC8201DL

The following tasks are required to be done by the station manager to use the power saving ActiPHYTM feature:

1. Setting the squelch level:

As per IEEE standard 802.3 MII register 22:11 and 22:10 set the squelch levels for 10Base-T operation. In addition to the 10BASE-

T squelch level control, the VSC8201 uses these bits to control the ActiPHYTM squelch levels. This is summarized in the following

table:

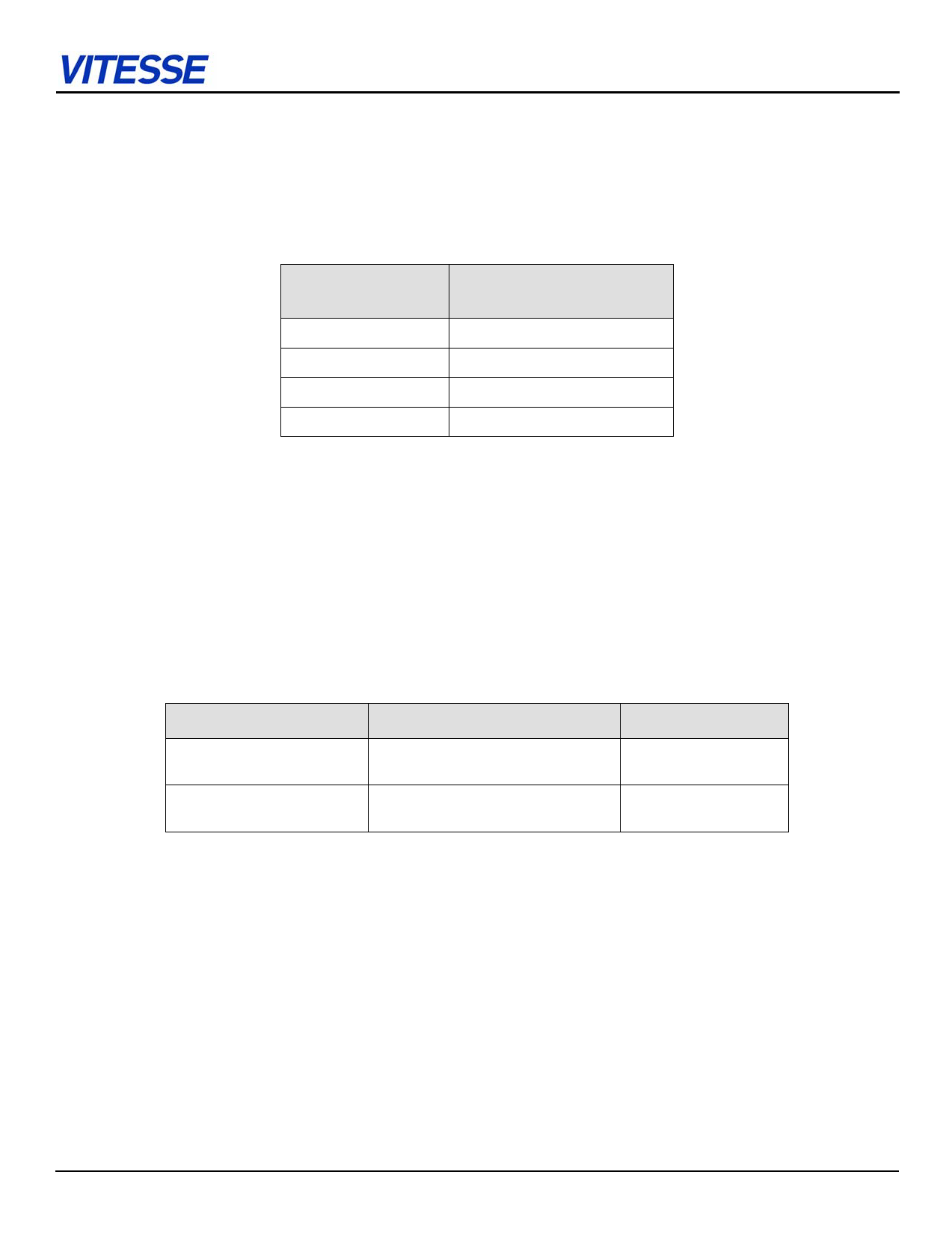

Table 4: 10BASE-T/ActiPHYTM squelch levels

Register Bit Setting

22:11:10

10BASE-T/ActiPHYTM

squelch level

00

Normal Squelch

01

Low squelch

10

High squelch

11

Reserved

2. Enabling the interrupt pin:

The VSC8201 conveys the valid signal detect signal via the MDINT# pin. In order to enable the MDINT# pin the station manager

must set the MII register 25:15.

3. Enabling the ActiPHYTM signal detect interrupt:

In ActiPHYTM mode MII register 25:13 i.e. the link state-change interrupt mask also acts as the ActiPHYTM signal detect interrupt

mask. This bit should be set to enable the ActiPHYTM signal detect interrupt. When a valid signal level is detected an interrupt

occurs and register 26:13 is set by the VSC8201 PHY. The MDINT# pin is pulled low.

4. Setting the PHY in ActiPHYTM mode:

The station manager can put the VSC8201 in ActiPHYTM mode by setting MII register 23:5. On setting register 23:5 the PHY goes

in one of the following power down states depending upon the state of the MII register 18:0

Table 5:

Register Bit Setting 18:0

Power down state

0

PLL disabled - 125MHz clock not

available on CLK125 pin

1

PLL enabled - 125MHz clock

available on CLK125 pin

a. Power dissipation figures are currently unavailable.

Power dissipationa

5. Coming out of ActiPHYTM mode:

The station manager responds to the interrupt signal by clearing the ActiPHYTM enable bit i.e. clears the register 23:5. When this bit

is cleared, all blocks of the PHY are powered up and the PHY reverts back to auto-negotiation and tries to establish a link. The sta-

tion manager should read MII register 26 to reset the interrupt status register.

Rev. 1.6.3 - 9/29/04

VITESSE - CONFIDENTIAL & PROPRIETARY - DO NOT COPY WITHOUT PERMISSION

- Page 6 of 21 -