UPD6464A Просмотр технического описания (PDF) - NEC => Renesas Technology

Номер в каталоге

Компоненты Описание

производитель

UPD6464A

UPD6464A Datasheet PDF : 52 Pages

| |||

µPD6464A,6465

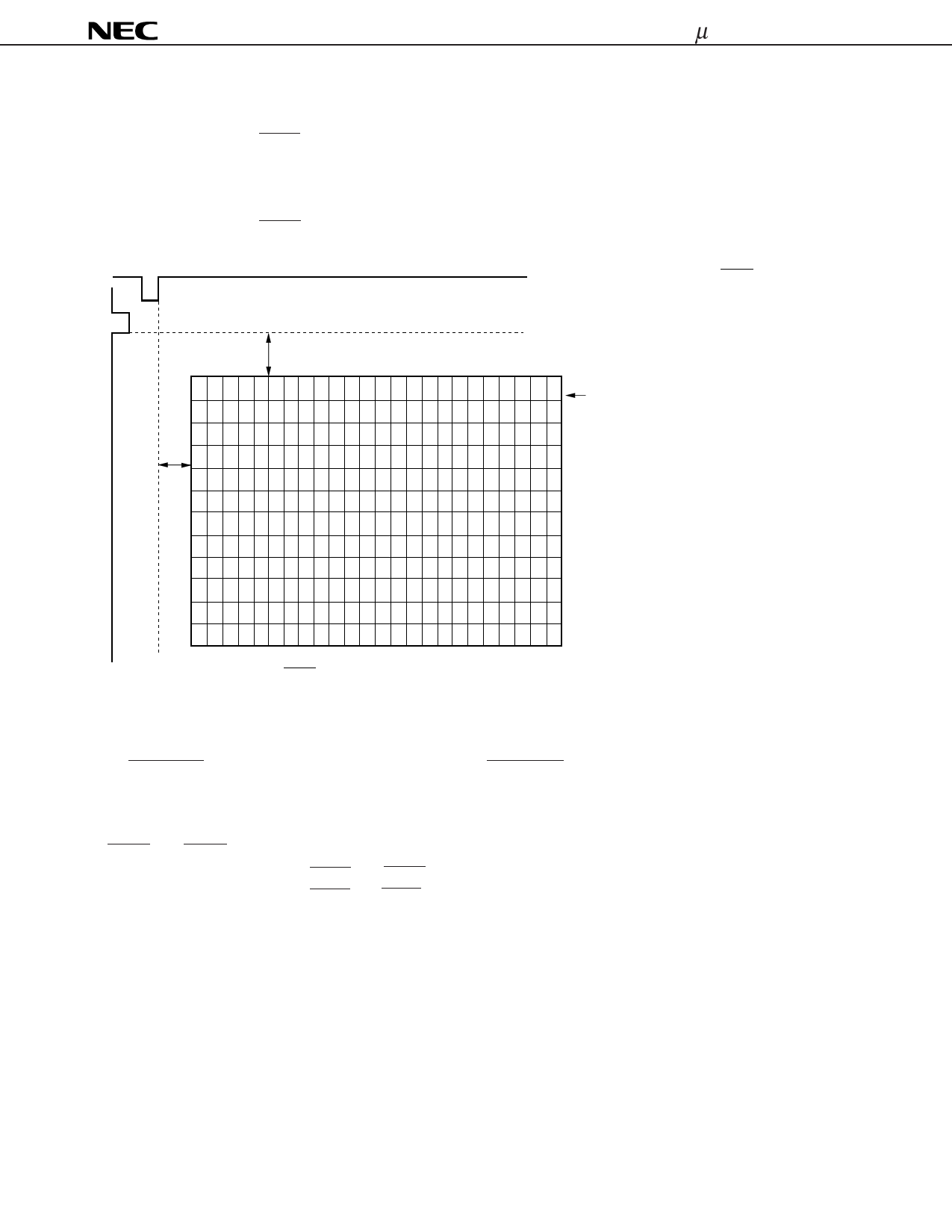

• Horizontal display start position control bits

The horizontal display start position can be set in 12-dot units and 32 steps, 16 clocks after the rising of the horizontal

synchronization signal (Hsync) (16/fOSC (MHz)).

• Vertical display start position control bits

The vertical display start position can be set in 9-line units and 32 steps, from the rising of the vertical

synchronization signal (Vsync).

Horizontal synchronization signal (Hsync)

A

B

Display area (12 lines × 24 columns)

Vertical synchronization signal (Vsync)

A: 9H (line) × (24V4 + 23V3 + 22V2 + 21V1 + 20V0)

12

B:

× (24H4 + 23H3 + 22H2 + 21H1 + 20H0) +

16

fOSC (MHz)

fOSC (MHz)

Remark fOSC: LC oscillation frequency (Dot Clock frequency)

Hsync and Vsync, which serve as references, are as follows:

Internal video signal mode : Hsync and Vsync are generated by internal circuit.

External video signal mode : Hsync and Vsync are generated from composite synchronization signal, input

to CSYN pin (pin 17), by sync. signal separation circuit.

18