TQ1090 Просмотр технического описания (PDF) - TriQuint Semiconductor

Номер в каталоге

Компоненты Описание

производитель

TQ1090 Datasheet PDF : 10 Pages

| |||

TQ1090

The phase relationship of the Group A outputs to Group

B and C are controlled by the phase-select pins S0 and

S1. The phase difference can be varied from –2t, –t, 0

or +t, where t = 1/fvco.

TriQuint’s patented output buffer design delivers a very

low output-to-output skew of 150 ps (max). The

TQ1090’s symmetrical TTL outputs are capable of

sourcing and sinking 30 mA.

Functional Description

The core of the TQ1090 is a Phase-Locked Loop (PLL)

that continuously compares the reference clock

(REFCLK) to the feedback clock (FBIN), maintaining a

zero frequency difference between the two. Since one

of the outputs is always connected to FBIN, the PLL

keeps the propagation delay between the outputs and

the reference clock within –350 ps +500 ps for the

TQ1090-MC500, and within –350 ps +700 ps for the

TQ1090-MC700.

The internal Voltage-Controlled Oscillator (VCO), has an

operating range of 260 MHz to 360 MHz, as shown in

Table 1. The combination of the VCO and the Divide

Logic enables the TQ1090 to operate between 33 MHz

and 45 MHz, 65 MHz and 90 MHz, and from 130 MHz

to 180 MHz.

The Shift Select pins, S0 and S1, control the phase

shift of the Group A outputs (Q0 – Q4), relative to the

other outputs. The user can select from four

incremental phase shifts as shown in Table 2 (Phase

Selection). The phase shift increment (t) is calculated

using the following equation, where n is the divide

mode:

t=

1

(fREF) (n)

In the test mode, the PLL is bypassed and REFCLK is

connected directly to the Divide Logic block via the

MUX, as shown in Figure 1. This mode is useful for

debug and test purposes. The test mode is outlined

in Table 3.

The maximum rise and fall time at the output pins is 1.4

ns. All outputs of the TQ1090 are TTL-compatible with

30 mA symmetric drive and a minimum VOH of 2.4 V.

Power-Up/Reset Synchronization

After power-up or reset, the PLL requires time before it

achieves synchronization lock. The maximum time

required for synchronization (TSYNC) is 500 ms.

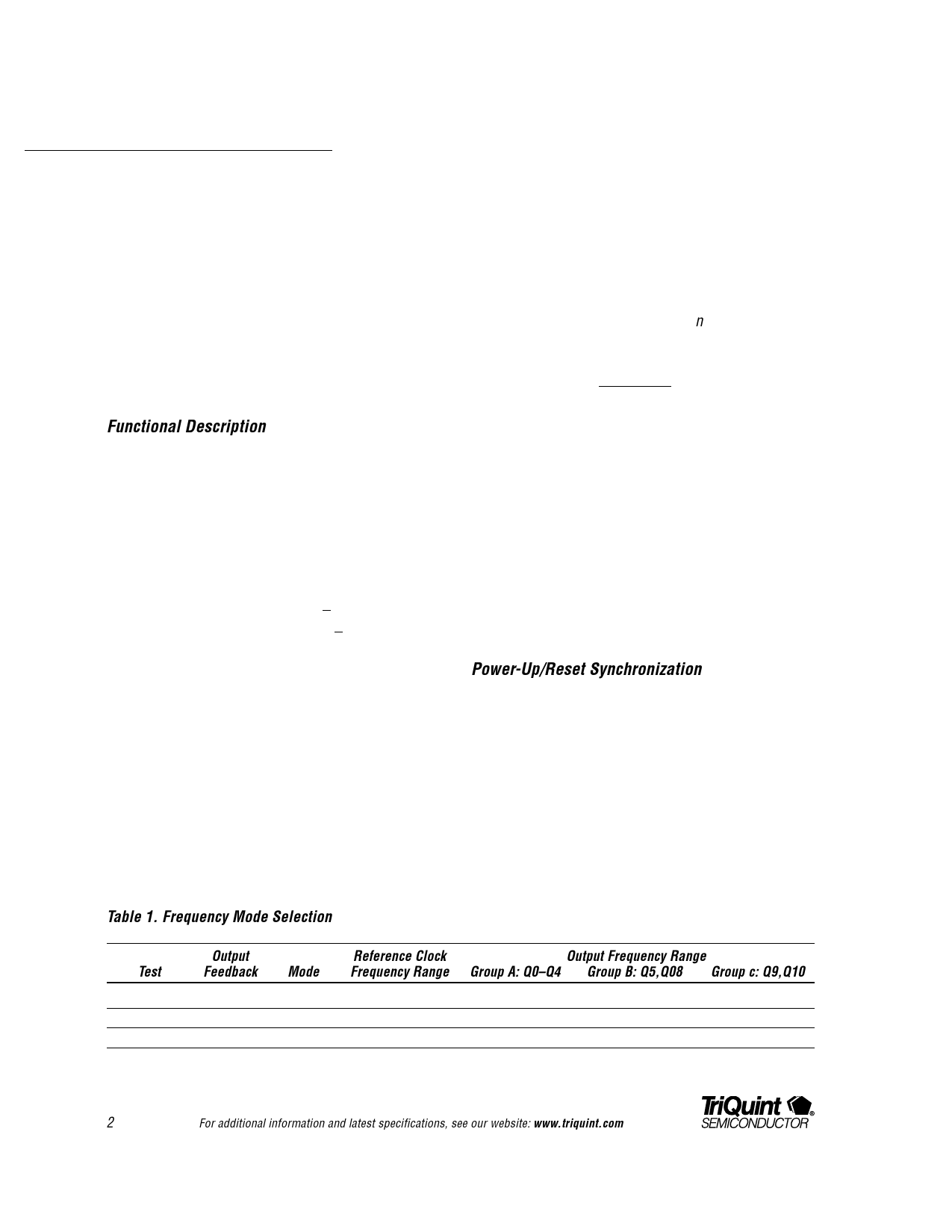

Table 1. Frequency Mode Selection

Output

Reference Clock

␣ Output Frequency Range

Test

Feedback Mode Frequency Range Group A: Q0–Q4 Group B: Q5,Q08 Group c: Q9,Q10

0

Group A

÷8

35 MHz – 45 MHz 35 MHz – 45 MHz

65 MHz – 90 MHz

130 MHz – 180 MHz

0

Group B

÷4

65 MHz – 90 MHz 35 MHz – 45 MHz

65 MHz – 90 MHz

130 MHz – 180 MHz

0

Group C

÷2

130 MHz – 180 MHz 35 MHz – 45 MHz

65 MHz – 90 MHz

130 MHz – 180 MHz

2

For additional information and latest specifications, see our website: www.triquint.com