TMC2072KHC Просмотр технического описания (PDF) - Fairchild Semiconductor

Номер в каталоге

Компоненты Описание

производитель

TMC2072KHC Datasheet PDF : 21 Pages

| |||

TMC2072

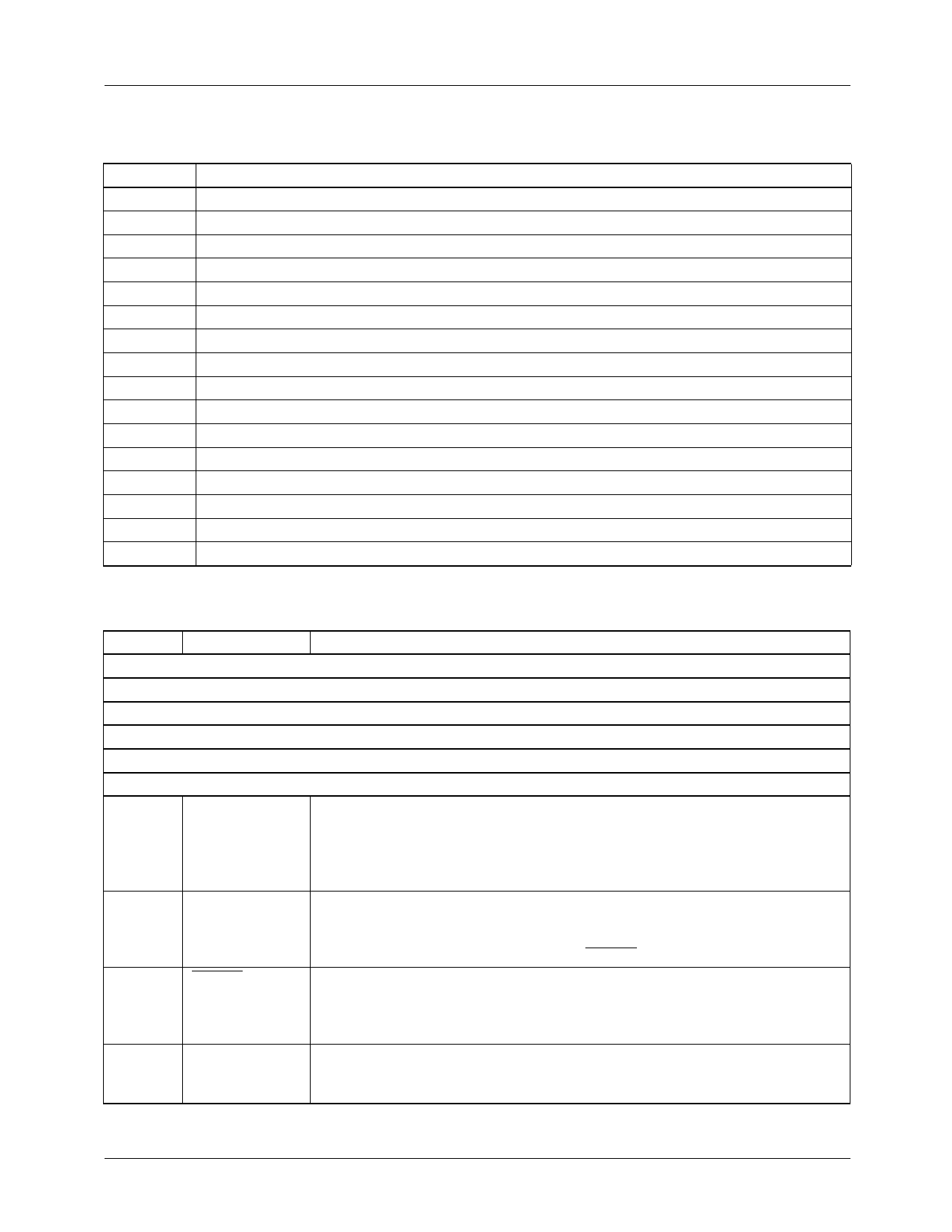

Control and Status Register Bit Functions

Summary

Register

Reg 00

Reg 01

Reg 02

Reg 03

Reg 04

Reg 05

Reg 06

Reg 07

Reg 08

Reg 09

Reg 0A

Reg 0B

Reg 0C

Reg 0D

Reg 0E

Reg 0F

Function

97h (year of revision)

read only

20h (part #)

read only

72h (part #)

read only

01h (silicon revision #)

read only

Reserved

Lock flags; sync tip

read only

Blank level

read only

Reserved

Format; clock rate; freerun; clamp; reset

HSync lead/lag

Gain; loop filter bandwidth; subpixel sync & clk position

Video source select

Vsync delay

Sync tip set

Output timing, tristate

Reserved

PRODUCT SPECIFICATION

Details

Bit

Name

Function

Reg 00 97h (year of revision)

Read Only

Reg 01 20h (part #)

Read Only

Reg 02 72h (part #)

Read Only

Reg 03 01h (silicon revision #)

Read Only

Reg 04 Reserved

Reg 05 Lock Flags & Sync Height

Read Only

7

BURST_DET

Each time a high-frequency signal is detected during a video line’s normal

expected burst interval, this flag goes high until the next line’s expected burst

period. If no high-frequency signal is present during the expected burst interval,

this flag goes low. With a standard color television signal input, this flag will be low

during vertical field groups and, in PAL, Bruch-blanked lines. [TMC22071A bit 47.]

6

BURST LOCK If the subcarrier loop is unlocked on the current video line, i.e., the subcarrier

phase error measured during burst exceeds the lock threshold, this flag goes low

until the next burst interval. If the phase error is less than the threshold, the flag is

reset high. This flag is meaningful only if HLOCK is low.

5

HLOCK

During each video field, if most horizontal sync pulses arrive more than 15 pixels

before or after their expected positions, this flag will go high. If most of the field’s

incoming horizontal syncs fall within 15 pixels of their expected positions, this flag

will go low. [TMC22071A bit 56.]

4:0

ST

These bits report the each line’s average sync tip level out of the A/D converter

(as observed over CVBS). For a clean signal, the reported value will match the

sync tip set in Reg 0D, below.

8

REV. 1.0.4 6/19/01