TFRA08C13 Просмотр технического описания (PDF) - Agere -> LSI Corporation

Номер в каталоге

Компоненты Описание

производитель

TFRA08C13 Datasheet PDF : 188 Pages

| |||

Preliminary Data Sheet

October 2000

TFRA08C13 OCTAL T1/E1 Framer

Functional Description (continued)

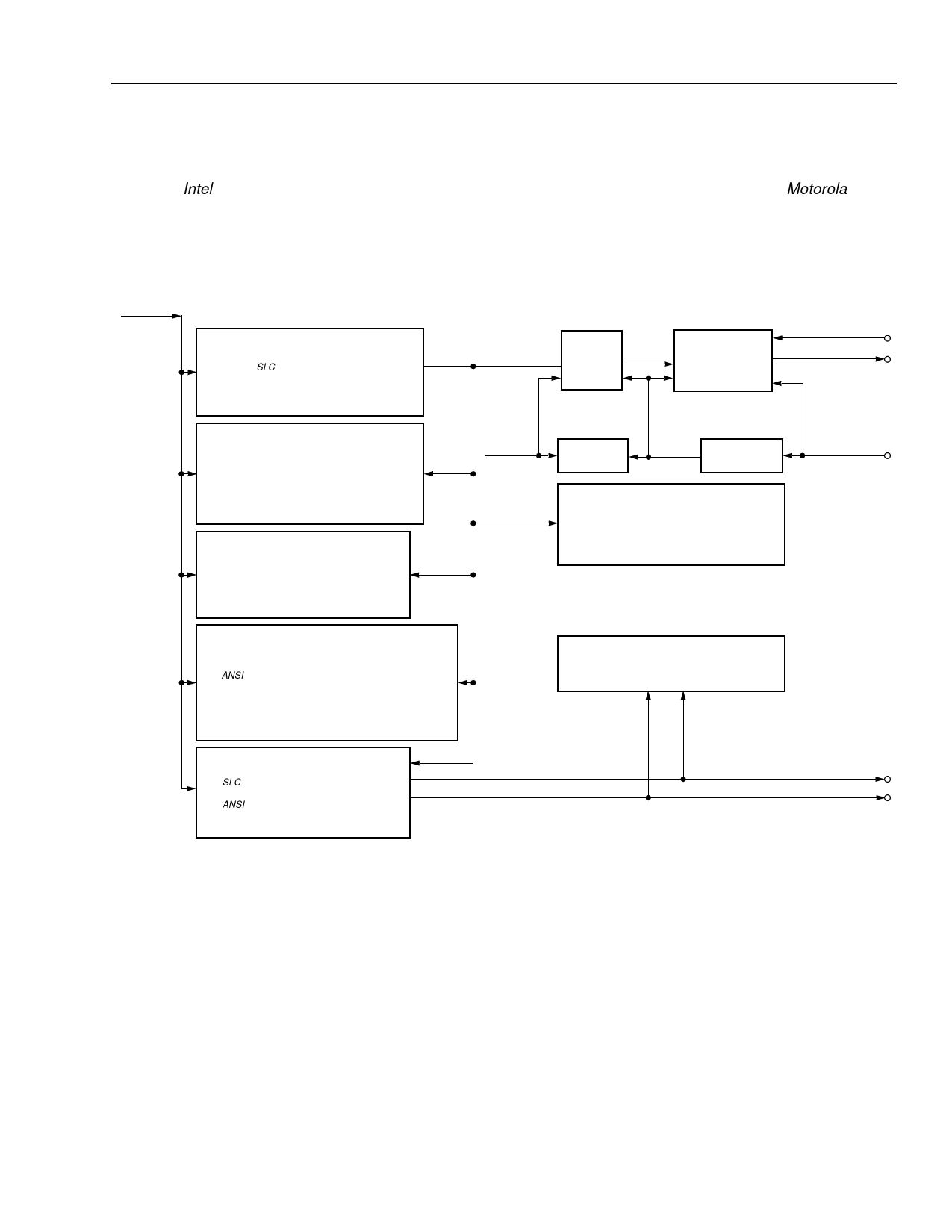

Accessing internal registers is done via the demultiplexed address and data bus microprocessor interface using

either the Intel 80188 (or 80X88) interface protocol with independent read and write signals or the Motorola

MC680X0 or M68360 interface protocol with address and data strobe signals.

The TFRA08C13 is manufactured using low-power CMOS technology and is packaged in an 352-pin plastic ball

grid array (PBGA) with 50 mils ball pitch.

RPD, RND_RBPV

RLCK

RECEIVE T1/E1 FRAME ALIGNMENT MONITOR,

REALIGNER, AND SYNC GENERATOR:

– SF: D4, SLC-96, DDS;

– ESF

– CEPT: BASIC FRAME, CRC-4 MULTIFRAME,

& SIGNALING MULTIFRAME

RECEIVE

ELASTIC

STORE

BUFFER

(2 FRAMES)

TRANSMIT

CONCENTRATION

HIGHWAY

INTERFACE

(RATE ADAPTER)

CHIFS

TCHIDATA/B

RECEIVE PERFORMANCE MONITOR:

– BIPOLAR VIOLATION ERRORS

– T1/E1 CRC ERRORS

– ERRORED EVENTS

– ERRORED SECONDS

– BURSTY ERRORED SECONDS

– SEVERELY ERRORED SECONDS

– UNAVAILABLE SECONDS

RECEIVE ALARM MONITOR:

– ANALOG LOSS OF SIGNAL

– DIGITAL LOSS OF SIGNAL

– REMOTE FRAME ALARM

– CEPT REMOTE MULTIFRAME ALARM

– ALARM INDICATION SIGNAL (AIS)

– SLIPS

RECEIVE PATTERN MONITOR:

– QUASI-RANDOM: 220 – 1

– PSEUDORANDOM: 215 – 1

– ANSI T1.403 BIT-ORIENTED AND ESF-FDL ACTIVATE

AND DEACTIVATE LINE LOOPBACK CODES

– CEPT AUXILIARY PATTERN (CEPT = 01)

– CEPT ACTIVATE AND DEACTIVATE LOOPBACK

CODES

– CEPT Sa6 CODES

RECEIVE FACILITY DATA LINK EXTRACTER

AND MONITOR:

– SLC-96 FORMAT

– DDS ACCESS

– ANSI T1.403-1989 ESF FORMAT:

• BIT-ORIENTED MESSAGES

• MESSAGE-ORIENTED MESSAGES

RFRMCK

RECEIVE SLIP

MONITOR

INTERNAL

SYSTEM CLOCK

RECEIVE SIGNALING EXTRACTER:

– DS1 ROBBED-BIT SIGNALING (RBS)

– CEPT CHANNEL ASSOCIATED AND

COMMON CHANNEL SIGNALING

– CONCENTRATION HIGHWAY ACCESS

– MICROPROCESSOR ACCESS

RECEIVE FDL HDLC EXTRACTER:

– 64-byte RECEIVE FIFO

– TRANSPARENT MODE (NO HDLC FRAMING)

– MICROPROCESSOR ACCESS

CHICK

RFDLCK

RFDL

5-6965(F)

Figure 2. TFRA08C13 Block Diagram: Receive Section (One of Eight Channels)

LLuucceenntt TTeecchhnnoollooggiieess IInncc..

13