TDA9901TS Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

производитель

TDA9901TS Datasheet PDF : 18 Pages

| |||

NXP Semiconductors

TDA9901

Wideband differential digital controlled variable gain amplifier

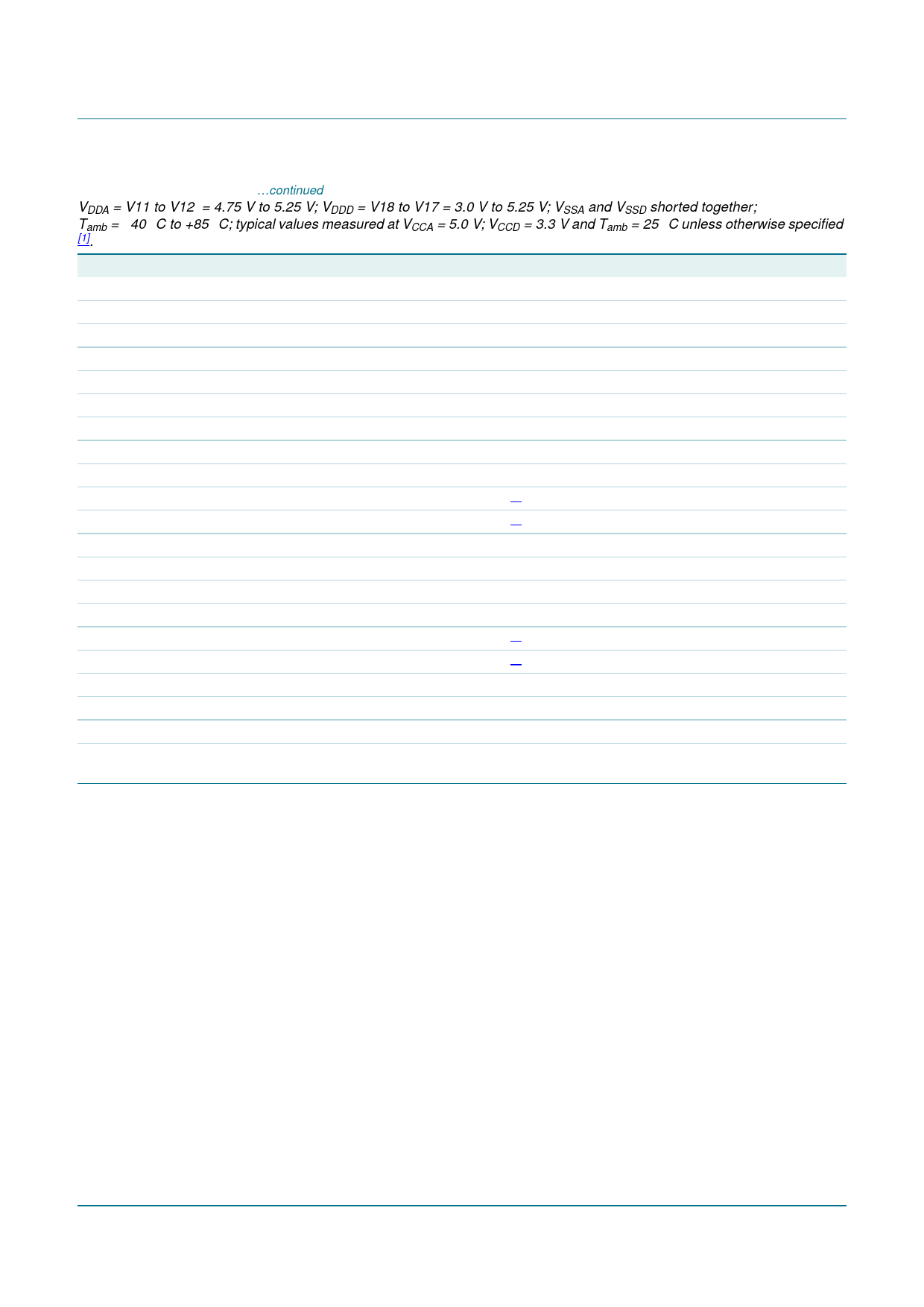

Table 6. Characteristics …continued

VDDA = V11 to V12 = 4.75 V to 5.25 V; VDDD = V18 to V17 = 3.0 V to 5.25 V; VSSA and VSSD shorted together;

Tamb = −40 °C to +85 °C; typical values measured at VCCA = 5.0 V; VCCD = 3.3 V and Tamb = 25 °C unless otherwise specified

[1].

Symbol Parameter

Conditions

Min

Typ

Max

Unit

tr

rise time

tf

fall time

Digital inputs: pins TE, GRAY0, GRAY1 and GRAY2

-

4.0

-

ns

-

4.0

-

ns

VIL

LOW-level input voltage

VIH

HIGH-level input voltage

IIH

HIGH-level input current

IIL

LOW-level input current

Ci

input capacitance

Clock inputs in TTL mode

0

-

2.0

-

−10

-

−10

-

-

-

0.8

V

VDDD

V

+10

µA

+10

µA

3

pF

VIL

LOW-level input voltage

VIH

HIGH-level input voltage

IIH

HIGH-level input current

IIL

LOW-level input current

Ci

input capacitance

Clock inputs in differential mode

[5] 0

-

[5] 2.0

-

15

-

−40

-

-

-

0.8

V

VDDD

V

80

µA

−10

µA

2

pF

VIL

LOW-level input voltage VDDA = 5.0 V

[6] 3.19

-

VIH

HIGH-level input voltage VDDA = 5.0 V

[6] 3.83

-

IIH

HIGH-level input current

15

-

IIL

LOW-level input current

−40

-

Ci

input capacitance

-

-

Vi(dif)(p-p)

peak-to-peak differential DC voltage level = 2.5 V

0.1

-

input voltage

3.52

V

4.12

V

80

µA

−5

µA

2

pF

2.0

V

[1] Due to the behavior of the on-chip regulator a warm-up time of 1 minute (typical) is recommended for optimal performance.

[2] The analog output voltages are positive with respect to VSSA.

[3] In latching mode (pin TE LOW), the gain settling is latched at the rising edge of the clock input.

[4] In transparent mode, the gain settling is directly controlled by the input data pattern.

[5] The circuit may be used with a single TTL clock on CLK or CLKN. The unused clock pin has to be decoupled to ground with a 100 nF

capacitance.

[6] There are four modes of operation for the clock inputs in non-TTL mode:

a) PECL mode 1: (DC level vary 1 : 1 with VDDA) CLK and CLKN inputs are differential PECL levels.

b) PECL mode 2: (DC level vary 1 : 1 with VDDA) CLK input is at PECL level and gain change takes place on the rising edge of the clock

input signal when in latched mode. A DC level of 3.65 V has to be applied on CLKN decoupled to VSSD via a 100 nF capacitor.

c) PECL mode 3: (DC level vary 1 : 1 with VDDA) CLKN input is at PECL level and gain change takes place on the rising edge of the

clock input signal when in latched mode. A DC level of 3.65 V has to be applied on CLK decoupled to VSSD via a 100 nF capacitor.

d) AC driving mode 4: when driving the CLK input directly and with any AC signal of minimum 0.1 V (p-p) and with a DC level of 2.5 V,

the gain change takes place on the rising edge of the clock signal. When driving the CLKN input with the same signal, gain change

takes place on the falling edge of the clock signal. NXP Semiconductors recommends decoupling of the CLKN or CLK input to VSSD

via a 100 nF capacitor.

TDA9901_4

Product data sheet

Rev. 04 — 14 August 2008

© NXP B.V. 2008. All rights reserved.

9 of 18