TDA9901TS Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

производитель

TDA9901TS Datasheet PDF : 18 Pages

| |||

NXP Semiconductors

TDA9901

Wideband differential digital controlled variable gain amplifier

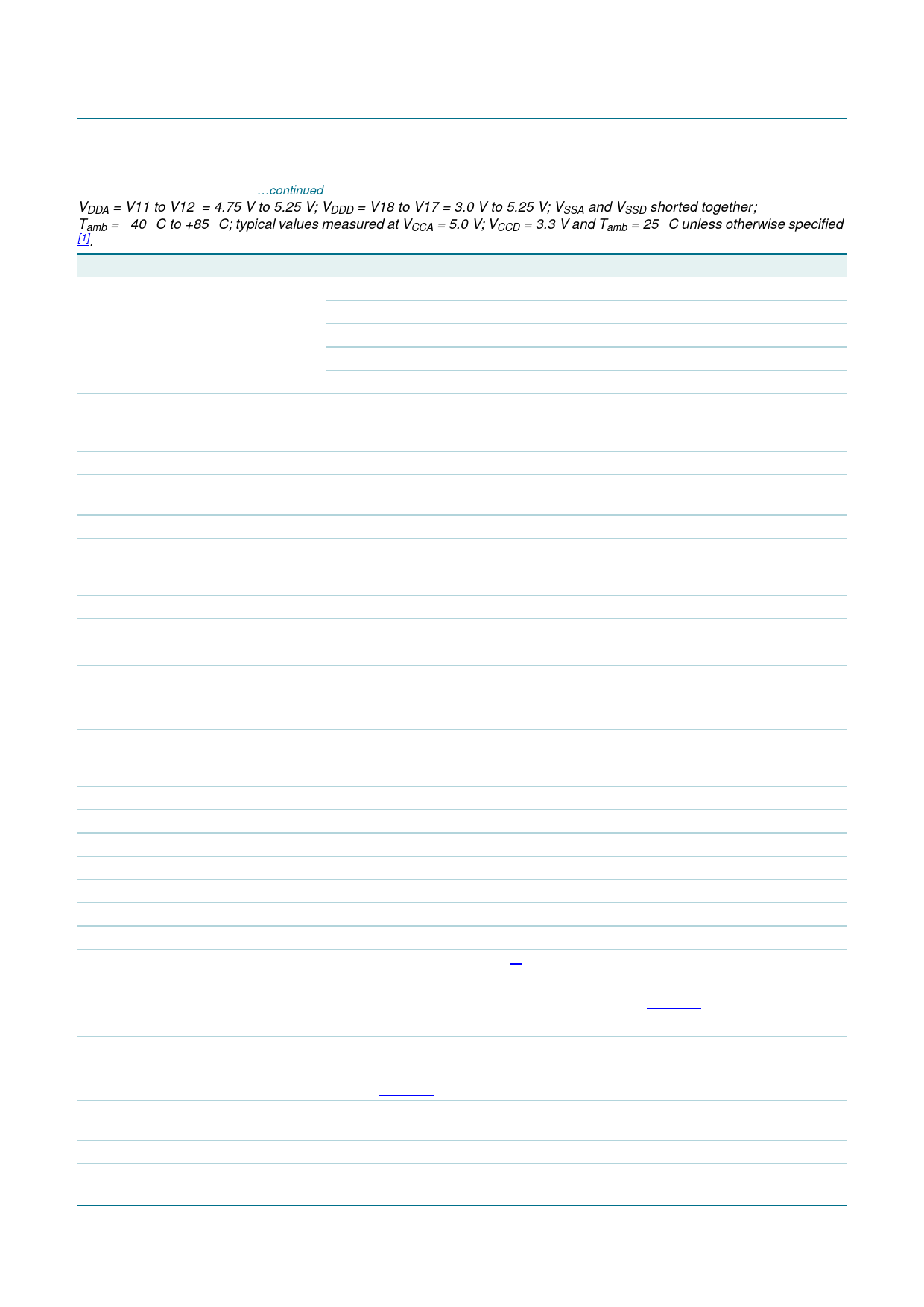

Table 6. Characteristics …continued

VDDA = V11 to V12 = 4.75 V to 5.25 V; VDDD = V18 to V17 = 3.0 V to 5.25 V; VSSA and VSSD shorted together;

Tamb = −40 °C to +85 °C; typical values measured at VCCA = 5.0 V; VCCD = 3.3 V and Tamb = 25 °C unless otherwise specified

[1].

Symbol Parameter

Conditions

Min

Typ

Max

Unit

α3H

third harmonic level

Vo = Vo(max); Tamb = 25 °C

fi = 0.5 MHz

-

fi = 4.43 MHz

-

fi = 12.5 MHz

-

fi = 21.4 MHz

-

∆α3H/∆T third harmonic level

fi = 21.4 MHz

-

variation with

temperature

−64

−60

dBc

−64

−59

dBc

−62

−58

dBc

−61

−57

dBc

80

-

mdB/°C

Reference voltage output ADC: pin CMADC

Vref

Ro

∆Vo(ref)/∆T

reference voltage

output resistance

reference output voltage

variation with

temperature

referenced to VDDA;

Tamb = 25 °C

Tamb = 25 °C

VDDA − 1.64 VDDA − 1.45 VDDA − 1.26 V

-

17

26

Ω

-

−0.11

-

mV/°C

Io(max)

maximum output current

Co

output capacitance

Reference voltage output VGA: pin CMVGA

-

1.0

-

mA

-

3

-

pF

Vref

Ro

∆Vo(ref)/∆T

reference voltage

output resistance

reference output voltage

variation with

temperature

referenced to VDDA;

Tamb = 25 °C

Tamb = 25 °C

VDDA − 2.48 VDDA − 2.30 VDDA − 2.17 V

-

9

20

Ω

-

1.75

-

mV/°C

Io(max)

maximum output current

-

1.0

-

mA

Co

output capacitance

-

3

-

pF

Gain switching characteristics (in latched mode); fclk = 52 MHz; Tamb = 25 °C; see Figure 3

th

hold time

2.0

-

-

ns

tsu

set-up time

3.8

-

-

ns

tw

pulse width

5.8

-

-

ns

tPD

propagation delay

-

ts

settling time

10 % to 90 % full scale if [3] -

±6 dB gain change

4.2

5.9

ns

2.6

3.2

ns

Gain switching characteristics (in transparent mode); fclk = 52 MHz; Tamb = 25 °C; see Figure 4

tPD

propagation delay

-

ts

settling time

10 % to 90 % full scale if [4] -

±6 dB gain change

6.7

9.5

ns

5.4

6.9

ns

Clock timing input: pins CLK and CLKN (see Figure 3)

fclk(max)

maximum clock

frequency

52

-

-

MHz

tw(clk)L

tw(clk)H

LOW clock pulse width

HIGH clock pulse width

4.0

-

-

ns

4.0

-

-

ns

TDA9901_4

Product data sheet

Rev. 04 — 14 August 2008

© NXP B.V. 2008. All rights reserved.

8 of 18