CXD1186CQ Просмотр технического описания (PDF) - Sony Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CXD1186CQ Datasheet PDF : 46 Pages

| |||

CXD1186CQ/CR

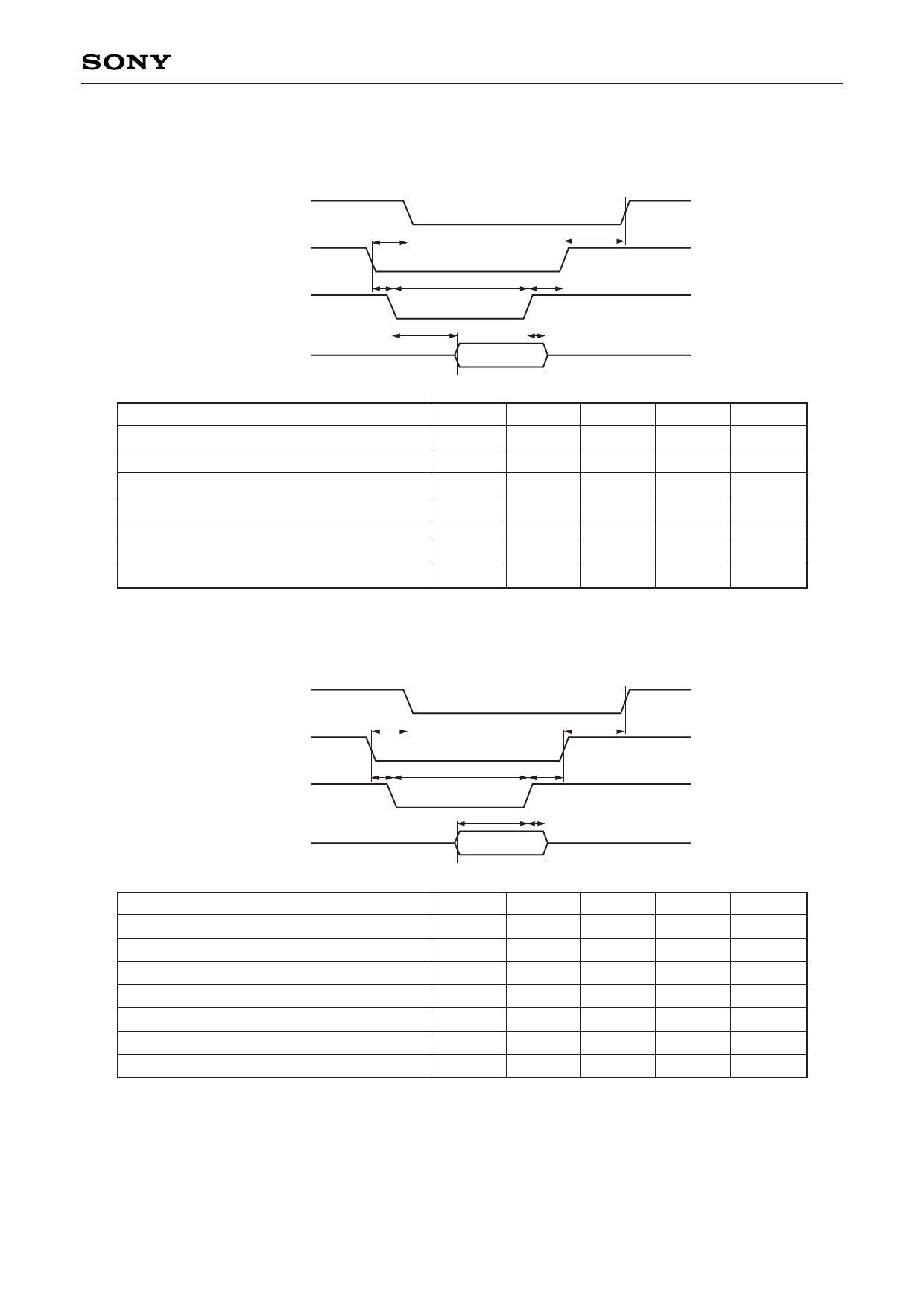

4. HOST DMA cycle (80 type bus)

(1) Read

HDRQ

XHAC

XHRD

HDB0 to 7, P

tDAR1

tSAR

tRRL

tDRD

tDAR2

tHRA

tFRD

Item

HDRQ fall time (vs. XHAC ↓)

HDRQ rise time (vs. XHAC ↑)

XHAC setup time (vs. XHRD ↓)

XHAC hold time (vs. XHRD ↑)

Low level XHRD pulse width

Data delay time (vs. XHRD ↓)

Data float time (vs. XHRD ↑)

Symbol Min.

Typ.

Max.

Unit

tDAR1

35

n

tDAR2

48

n

tSAR

5

n

tHRA

0

n

tRRL

100

n

tDRD

60

n

tFRD

0

10

n

(2) Write

HDRQ

XHAC

XHWR

tDAR1

tSAW

HDB0 to 7, P

tWWL

tSDW

tDAR2

tHWA

tHWD

Item

HDRQ fall time (vs. XHAC ↓)

HDRQ rise time (vs. XHAC ↑)

XHAC setup time (vs. XHWR ↓)

XHAC hold time (vs. XHWR ↑)

Low level XHWR pulse width

Data setup time (vs. XHWR ↑)

Data hold time (vs. XHWR ↑)

Symbol

tDAR1

tDAR2

tSAW

tHWA

tWWL

tSDW

tHWD

Min.

5

0

50

40

10

Typ.

Max.

35

48

Unit

n

n

n

n

n

n

n

—10—