SX1240 Просмотр технического описания (PDF) - Semtech Corporation

Номер в каталоге

Компоненты Описание

производитель

SX1240 Datasheet PDF : 20 Pages

| |||

ADVANCED COMMUNICATIONS & SENSING

SX1240

Integrated Transmitter IC

DATASHEET

3.2. Application Mode: Advanced

3.2.1. Advanced Mode: Configuration

Advanced mode can be accessed as described on Figure 3. Programming is performed via a two wire interface (TWI)

formed by CTRL and DATA pins.

Programming of the configuration register is triggered by a rising edge on the CTRL line. Upon detection of this rising edge,

the data applied to the DATA pin is accepted as register configuration information, the data bits are clocked on subsequent

rising edges of the clocking signal applied to the CTRL pin. The first bit of serial data selects register read or write operation

(Read = ‘high’ and Write = ‘low’). The timing for SX1240 configuration register ‘write’ is shown in Figure 5. Note that, once

triggered, all 13 data bits must be written to the SX1240.

The contents of the configuration register and the role of each bit therein is described in Table 8 of Section 4.

CTRL

DATA

R/W ACC D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

‘0’ ‘0’ ‘0’

Figure 5. TWI Configuration Register ‘Write’.

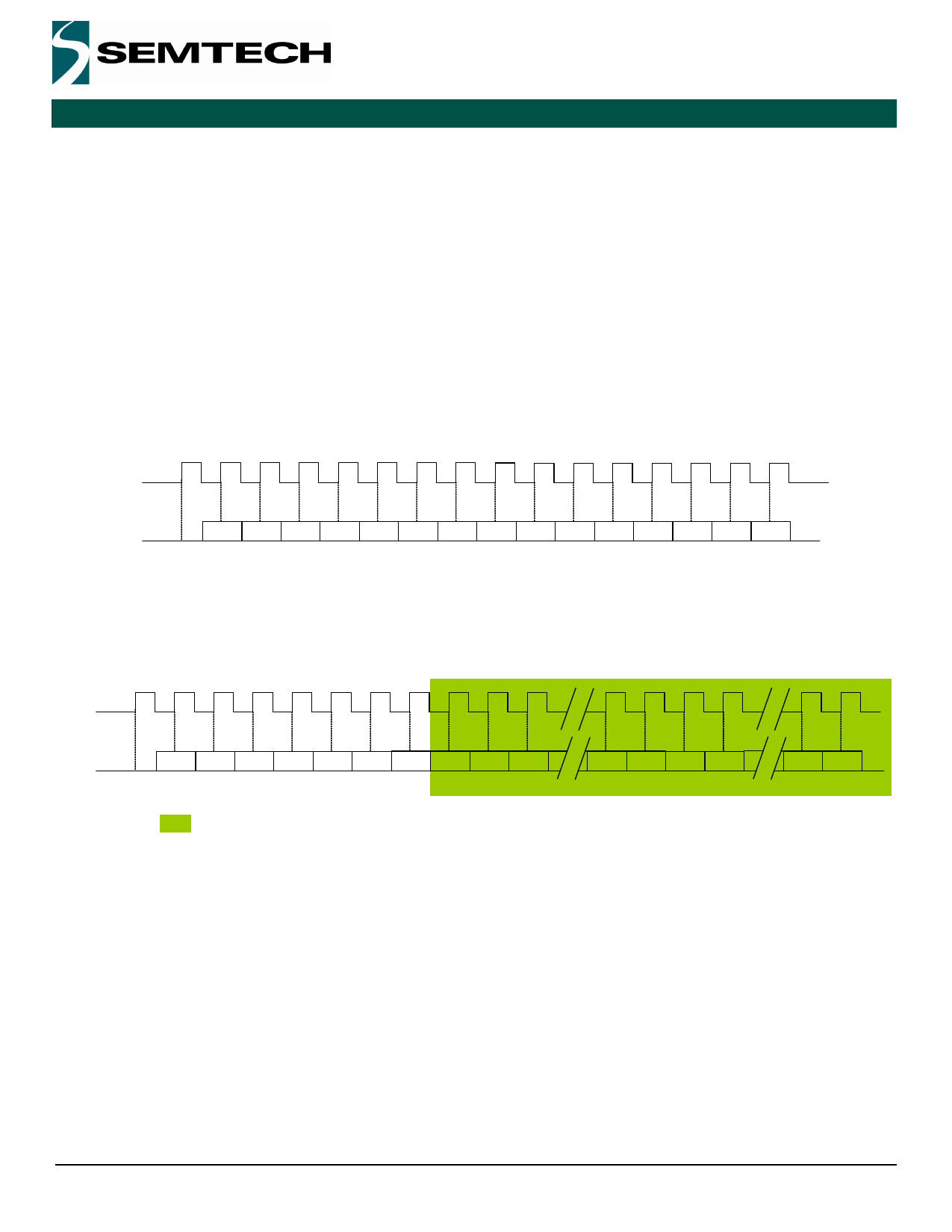

Similarly, the configuration register may be read using the timing of Figure 6.

CTRL

DATA

R/W ACC ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ D12 D11 D10

‘0’ ‘1’ ‘0’

D1 D0 T42 T41

DATA pin is an output

Figure 6. TWI Configuration Register ‘Read’.

T1 T0

Notes - Logic level ‘0’ on DATA during the first rising edge on CTRL is required to start the TWI access

- Reading only the 13 configuration bits D0 to D12 is not allowed on the SX1240. In Read access, 64 clock cycles

on CTRL pin must be issued, shifting out on pin DATA the 13 configuration bits (D0 to D12), plus 43 internal test

bits (T0 to T42). Read access should be used when developing the device firmware, but is not intended for use in

the normal operation mode.

- During the register ‘write’ or ‘read’ phases the SX1240 remains in sleep mode.

SX1240, Rev 1, Oct 2010

©2010 Semtech Corp.

Page 10

www.semtech.com