SP7800 –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ—Ö–Ω–∏—á–µ—Å–∫–æ–≥–æ –æ–ø–∏—Å–∞–Ω–∏—è (PDF) - Signal Processing Technologies

–ù–æ–º–µ—Ä –≤ –∫–∞—Ç–∞–ª–æ–≥–µ

–ö–æ–º–ø–æ–Ω–µ–Ω—Ç—ã –û–ø–∏—Å–∞–Ω–∏–µ

–ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç–µ–ª—å

SP7800 Datasheet PDF : 13 Pages

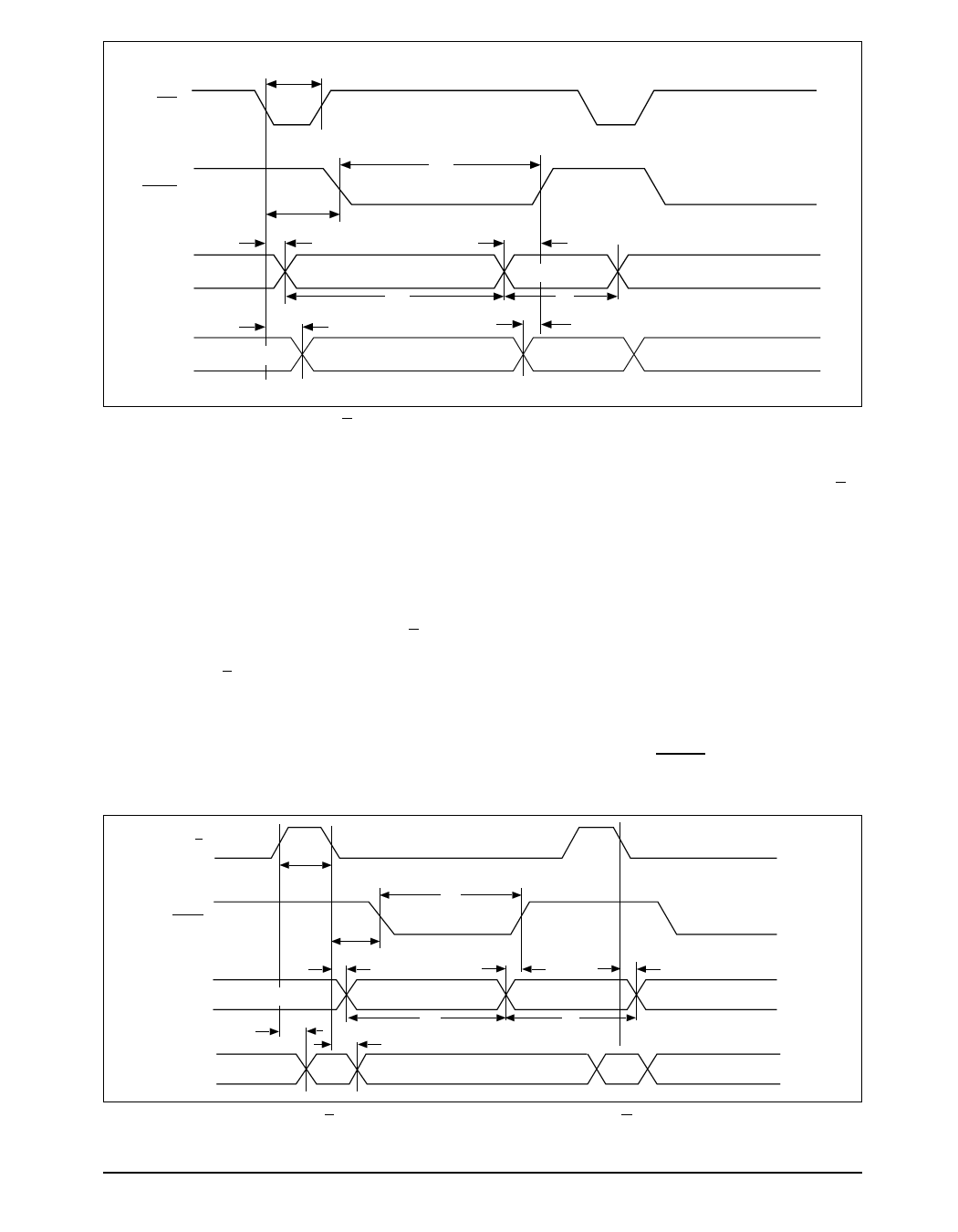

| |||

R/C

tW

BUSY

Converter

Mode

Data

BUS

tB

tDBC

Acquire

Data Valid

tAP

t DBE

Convert

tC

tHDR and tHL

Hi-Z State

Acquire

tA

t DB

Data Valid

Convert

Hi-Z State

Figure 5. Convert Mode Timing — R/C Pulse LOW, Outputs Enabled After Conversion

the SP7800A. These potential system problem sources

are particularly important to consider when develop-

ing a new system, and looking for the causes of errors

in breadboards.

First, care should be taken to avoid glitches during

critical times in the sampling and conversion process.

Since the SP7800A has an internal sample/hold func-

tion, the signal that puts it into the hold state (R/C going

LOW) is critical, as it would be on any sample/hold

amplifier. The R/C falling edge should be sharp (5 to

10ns), have low jitter and minimal ringing, especially

during the 20ns after it falls.

Although not normally required, it is also good prac-

tice to avoid glitches from coupling to the SP7800A

while bit decisions are being made. Since the above

discussion calls for a fast, clean rise and fall on R/C, it

makes sense to keep the rising edge of the convert

pulse outside the time when bit decisions are being

made. In other words, the convert pulse should either

be short (under 100ns so that it transitions before the

MSB decision), or relatively long (over 2.75µs to

transition after the LSB decision).

Next, although the data outputs are forced into a Hi-Z

state during conversion, fast bus transients can still be

capacitively coupled into the SP7800A. If the data bus

experiences fast transients during conversion, these

transients can be attenuated by adding a logic buffer to

the data outputs. The BUSY output can be used to

enable the buffer.

R/C

tW

BUSY

Converter

Mode

Data

BUS

tB

tDBC

Acquire

tDD

Hi-Z State

Data

Valid

tAP

t DBE

Convert

tC

tHDR and tHL

Hi-Z State

Acquire

tA

tAP

Convert

Data

Valid

Hi-Z State

Figure 6. Read Mode Timing — R/C Pulse HIGH, Outputs Enabled Only When R/C is High

SP7800ADS/02

SP7800A 12-Bit 3µs Sampling A/D Converter

9

© Copyright 2000 Sipex Corporation