ADV473KP135 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADV473KP135 Datasheet PDF : 12 Pages

| |||

ADV473

VIDEO MODES

24-Bit True-Color Mode

Twenty-four bits of RGB color information may be input into

the ADV473 every clock cycle. The 24 bits of pixel information

are input via the R0–R7, G0–G7, and B0–B7 inputs. R0–R7 ad-

dress the red color palette RAM, G0–G7 address the green

color palette RAM, and B0–B7 address the blue color palette

RAM. Each RAM provides 8 bits of color information to the

corresponding D/A converter. The pixel read mask register is

used in this mode.

24-Bit True-Color Bypass Mode

Twenty-four bits of pixel information may be input into the

ADV473 every clock cycle. The 24 bits of pixel information are

input via the R0–R7, G0–G7, and B0–B7 inputs. R0–R7 drive

the red DAC directly, G0–G7 drive the green DAC directly,

and B0–B7 drive the blue DAC directly. The color palette

RAMs and pixel read mask register are bypassed.

8-Bit Pseudo-Color Mode

Eight bits of pixel information may be input into the ADV473

every clock cycle. The 8 bits of pixel information (P0–P7) are

input via the R0–R7, G0–G7 or B0–B7 inputs, as specified by

CR7 and CR6. All three color palette RAMs are addressed by

the same 8 bits of pixel data (P0–P7). Each RAM provides 8

bits of color information to the corresponding D/A converter.

The pixel read mask register is used in this mode.

8-Bit True-Color Bypass Mode

Eight bits of pixel information may be input into the ADV473

every clock cycle. The 8 bits of pixel information are input via

the R0–R7, G0–G7 or B0–B7 inputs, as specified by CR7 and

CR6.

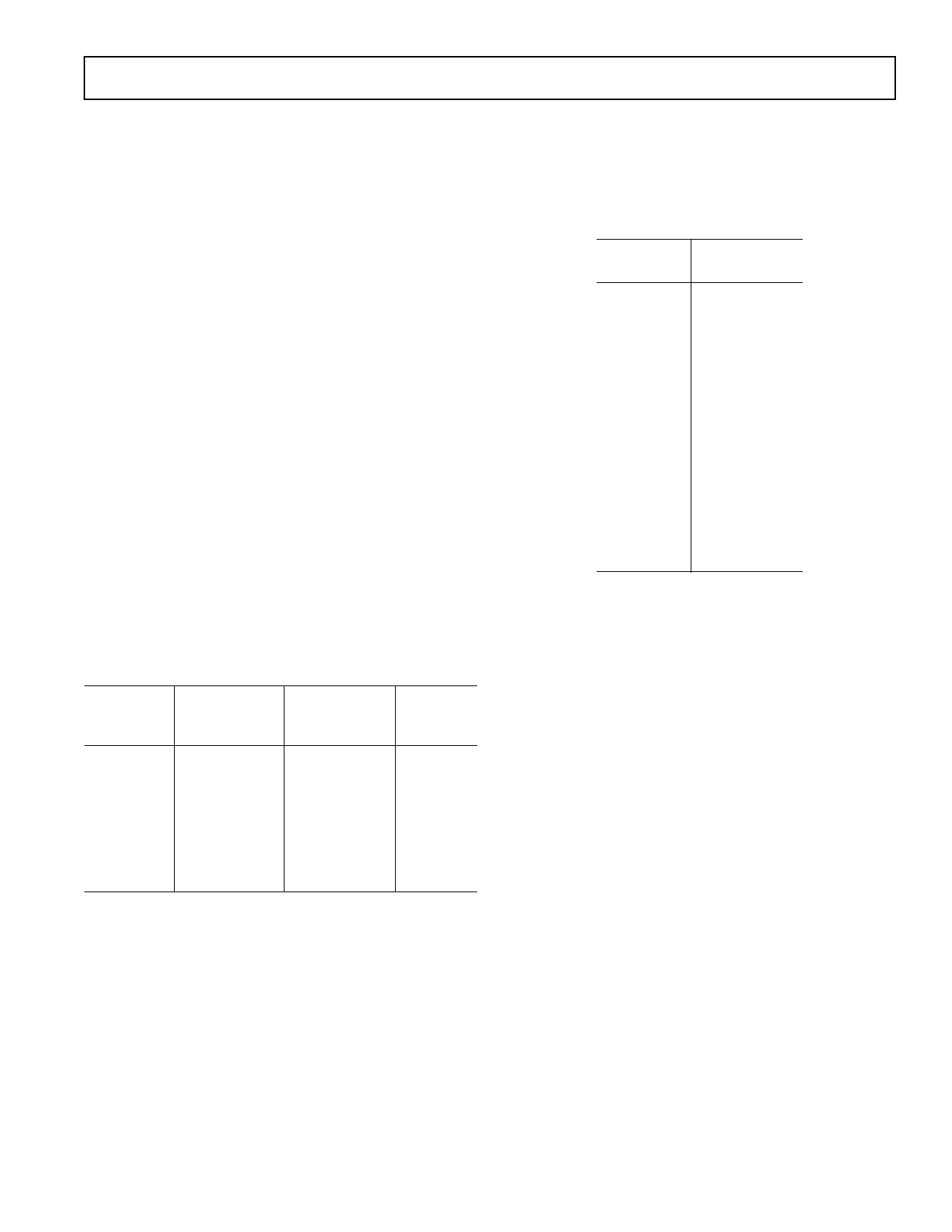

Table IV. 8-Bit True-Color Bypass Video Input Format

R0–R7

Inputs

Selected

G0–G7

Inputs

Selected

B0–B7

Input

Selected

Inputs

Format

R7

G7

R6

G6

R5

G5

R4

G4

R3

G3

R2

G2

R1

G1

R0

G0

B7

R7

B6

R6

B5

R5

B4

G7

B3

G6

B2

G5

B1

B7

B0

B6

As seen in the table, 3 bits of red, 3 bits of green, and 2 bits of

blue data are input. The 3 MSBs of the red and green DACs are

driven directly by the inputs, while the 2 MSBs of the blue DAC

are driven directly. The 5 LSBs for the red and green DACs,

and the 6 LSBs for the blue DAC, are a logical zero. The color

palette RAMs and pixel read mask register are bypassed.

15-Bit True-Color Bypass Mode

Fifteen bits of pixel information may be input into the ADV473

every clock cycle. The 15 bits of pixel information (5 bits of red,

5 bits of green, and 5 bits of blue) are input via the R0–R7 and

G0–G7 inputs.

Table V. 15-Bit True-Color Video Input Format

Pixel

Inputs

Input

Format

R7

0

R6

R7

R5

R6

R4

R5

R3

R4

R2

R3

R1

G7

R0

G6

G7

G5

G6

G4

G5

G3

G4

B7

G3

B6

G2

B5

G1

B4

G0

B3

The 5 MSBs of the red, green, and blue DACs are driven di-

rectly by the inputs. The 3 LSBs are a logical zero. The color

palette RAMs and pixel read mask register are bypassed.

15-Bit True-Color Mode

Fifteen bits of pixel information may be input into the ADV473

every clock cycle. The 15 bits of pixel information are input to

the device via R0–R7 and G0–G7 according to Table V. This

input data points to the top 32 locations of the color palette

RAM, i.e., locations 223 to 255. The 15-bit pixel input data in-

dexes a 24-bit red, green and blue value which is clocked to the

three DACs.

Overlays

The overlay inputs, OL0–OL3, have priority regardless of the

color mode as shown in Table III.

Pixel Read Mask Register

The 8-bit pixel read mask register is implemented as three 8-bit

pixel read mask registers, one each for the R0–R7, G0–G7, and

B0–B7 inputs. When writing to the pixel read mask register, the

same data is written to all three registers. The read mask regis-

ters are located just before the color palette RAMs. Thus, they

are used only in the 24-bit true-color and 8-bit pseudo-color

modes since these are the only modes that use the color palette

RAMs.

The contents of the pixel read mask register, which may be

accessed by the MPU at any time, are bit-wise logically ANDed

with the 8-bit inputs prior to addressing the color palette RAMs.

Bit D0 of the pixel read mask register corresponds to pixel input

P0 (R0, G0, or B0 depending on the mode). Bit D0 also corre-

sponds to data bus Bit D0.

REV. A

–9–