SI5316 Просмотр технического описания (PDF) - Silicon Laboratories

Номер в каталоге

Компоненты Описание

производитель

SI5316 Datasheet PDF : 16 Pages

| |||

Si5316

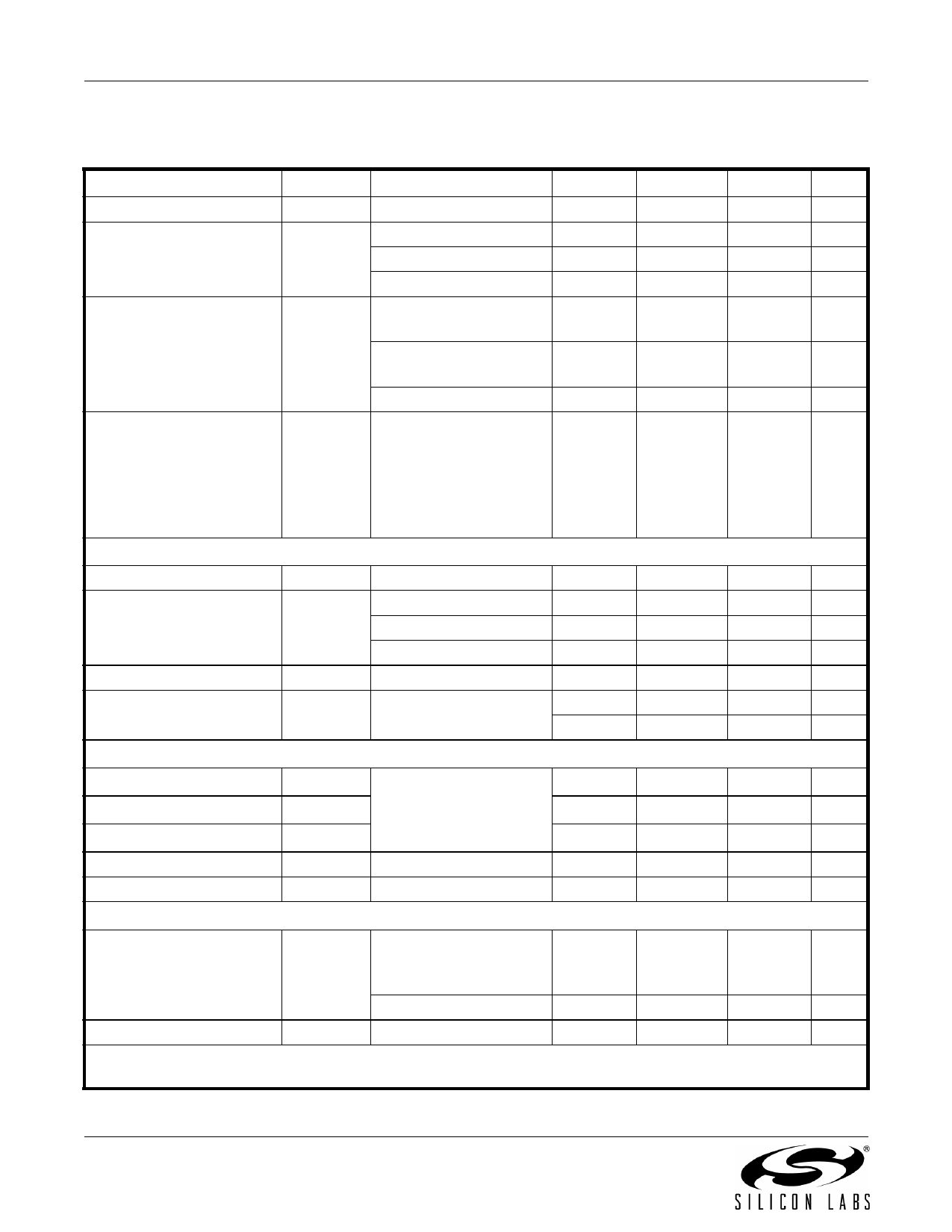

Table 1. Performance Specifications

(VDD = 1.8, 2.5, or 3.3 V ±10%, TA = –40 to 85 ºC)

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

Temperature Range

TA

Supply Voltage

VDD

Supply Current

IDD

Input/Output Clock Fre-

CKF

quency (CKIN1, CKIN2,

CKOUT)

Input Clocks (CKIN1, CKIN2)

fOUT = 622.08 MHz

LVPECL format output

fOUT = 19.44 MHz

CMOS format output

Tristate/Sleep Mode

FRQSEL[1:0] = LL

FRQSEL[1:0] = LM

FRQSEL[1:0] = LH

FRQSEL[1:0] = ML

FRQSEL[1:0] = MM

FRQSEL[1:0] = MH

–40

2.97

2.25

1.62

—

—

—

19.38

38.75

77.5

155.0

310.0

620.0

25

3.3

2.5

1.8

217

194

TBD

—

—

—

—

—

—

85

ºC

3.63

V

2.75

V

1.98

V

243

mA

220

mA

TBD

22.28

44.56

89.13

178.25

356.5

710.0

mA

MHz

Differential Voltage Swing

Common Mode Voltage

CKNDPP

CKNVCM

1.8V ±10%

2.5V ±10%

0.25

—

0.9

—

1.0

—

1.9

VPP

1.4

V

1.7

V

3.3V ±10%

1.1

—

1.95

V

Rise/Fall Time

Duty Cycle

CKNTRF

20–80%

—

—

11

ns

CKNDC

Whichever is less

40

—

60

%

50

—

—

ns

Output Clock (CKOUT)

Common Mode

Differential Output Swing

Single Ended Output Swing

Rise/Fall Time

Duty Cycle

PLL Performance

VOCM

VOD

VSE

CKOTRF

CKODC

LVPECL

100 Ω load

line-to-line

20–80%

VDD – 1.42

—

VDD – 1.25 V

1.1

—

1.9

VPP

0.5

—

0.93

V

—

230

350

ps

45

—

55

%

Jitter Generation

JGEN

fOUT = 622.08 MHz,

—

LVPECL output format

50 kHz–80 MHz

0.3

TBD ps rms

12 kHz–20 MHz

—

0.3

TBD ps rms

Jitter Transfer

JPK

—

0.05

0.1

dB

Note: For a more comprehensive listing of device specifications, please consult the Silicon Laboratories Any-Rate Precision

Clock Family Reference Manual. This document can be downloaded from www.silabs.com/timing.

2

Preliminary Rev. 0.24