RTL8130 Просмотр технического описания (PDF) - Realtek Semiconductor

Номер в каталоге

Компоненты Описание

производитель

RTL8130 Datasheet PDF : 55 Pages

| |||

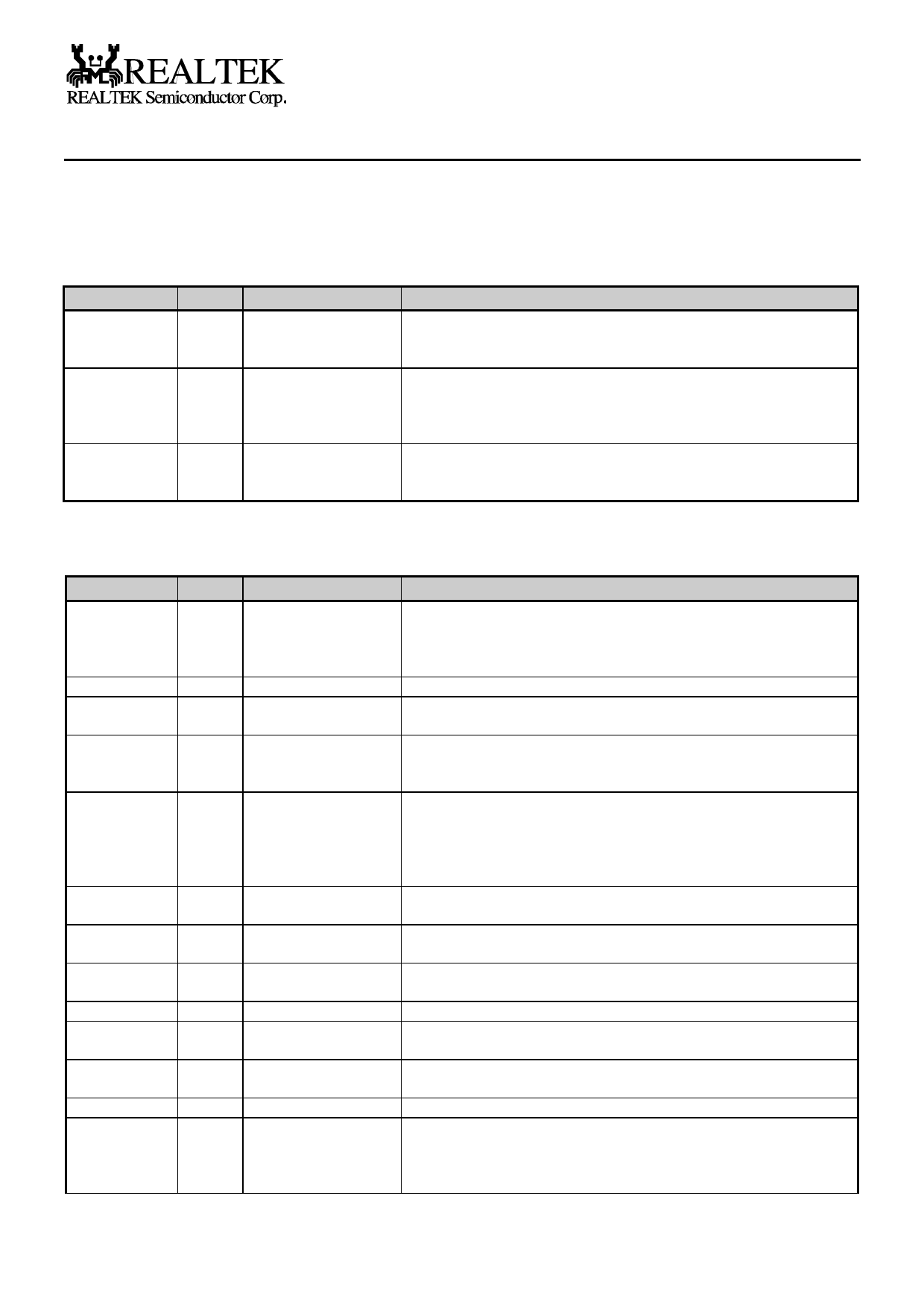

4. Pin Descriptions

RTL8130 Preliminary

4.1 Power Management/Isolation Interface(3 pins)

Symbol

PMEB

(PME#)

ISOLATEB

(ISOLATE#)

Type

O/D

I

LWAKE

O

Pin No

98

71

59

Description

Power Management Enable: Open drain, active low. Used by the

RTL8130 to request a change in its current power management state

and/or to indicate that a power management event has occurred.

Isolate pin: Active low. Used to isolate RTL8130 from the PCI bus.

The RTL8130 does not drive its PCI outputs (excluding PME#) and

does not sample its PCI input (including RST# and PCICLK) as long

as Isolate pin is asserted.

LAN WAKE-UP pin: Active high. Used to inform the motherboard to

execute wake-up process in LAN WAKE-UP mode. (Magic packet

only)

4.2 PCI Interface(50 pins)

Symbol

AD31-0

C/BE3-0

CLK

DEVSELB

FRAMEB

GNTB

REQB

IDSEL

INTAB

IRDYB

TRDYB

PAR

PERRB

Type

T/S

T/S

I

S/T/S

S/T/S

I

T/S

I

O/D

S/T/S

S/T/S

T/S

S/T/S

Pin No

108-111, 113-116,

120-121, 123-127, 129,

142-145, 147-150,

153-155, 157-160, 1

118, 130, 140, 152

104

135

131

105

106

119

102

132

133

139

137

Description

PCI address and data multiplexed pins

PCI bus command and byte enables multiplexed pins

Clock provides timing for all transactions on PCI and is input to PCI

device.

Device Select: When actively driven, indicates the RTL8130 has

decoded its address as the target of the current access, As an input,

DEVSELB indicates whether any device on the bus has been selected.

Cycle Frame is driven by the current master to indicate the beginning

and duration of an access. FRAMEB is asserted to indicated a bus

transaction is beginning. While FRAMEB is asserted, data transfers

continue. When FRAMEB is deasserted, the transaction is in the final

data phase.

Grant: This signal is asserted low to indicate the RTL8130 that has

been granted to access to the bus.

Request: The RTL8130 will assert this signal low to request to access

to the bus.

Initialization Device Select is used as a chip select during

configuration read and write transactions.

INTAB is used to request an interrupt.

Initiator Ready indicates the initiating agent's ability to complete the

current data phase of the transaction.

Target Ready indicates the target agent's ability to complete the

current phase of the transaction.

Parity is even parity across AD31-0 and C/BE3-0.

Parity Error: When the RTL8130 is in bus master access mode and a

parity error is detected, the RTL8130 asserts both SERR bit in ISR

and Configuration Space command bit 8 (SERRB enable). Next, it

completes the current data burst transaction, then stops operation and

1999/5/30

5

Ver.1.1