LH28F800SU –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ—Ö–Ω–∏—á–µ—Å–∫–æ–≥–æ –æ–ø–∏—Å–∞–Ω–∏—è (PDF) - Sharp Electronics

–ù–æ–º–µ—Ä –≤ –∫–∞—Ç–∞–ª–æ–≥–µ

–ö–æ–º–ø–æ–Ω–µ–Ω—Ç—ã –û–ø–∏—Å–∞–Ω–∏–µ

–ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç–µ–ª—å

LH28F800SU Datasheet PDF : 38 Pages

| |||

LH28F800SU

8M (512K √ó 16, 1M √ó 8) Flash Memory

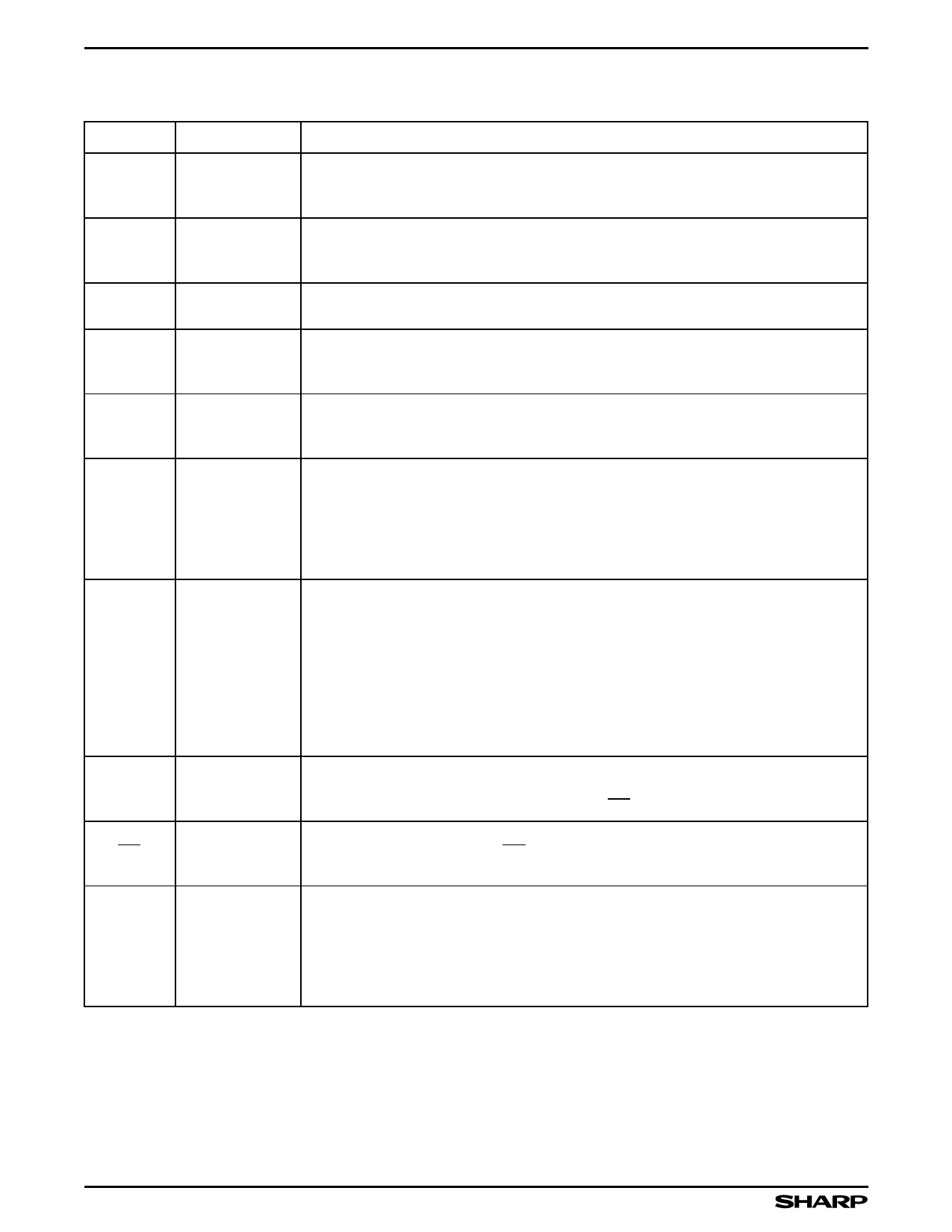

PIN DESCRIPTION

SYMBOL

TYPE

NAME AND FUNCTION

A0

INPUT

A1 - A15 INPUT

BYTE-SELECT ADDRESS: Selects between high and low byte when device is in x8

mode. This address is latched in x8 Data Writes. Not used in x16 mode (i.e., the

A0 input buffer is turned off when BYTE is high).

WORD-SELECT ADDRESSES: Select a word within one 64K block. A6 - A15 selects

1 of 1024 rows, and A1 - A5 selects 16 of 512 columns. These addresses are

latched during Data Writes.

A16 - A19 INPUT

BLOCK-SELECT ADDRESSES: Select 1 of 16 Erase blocks. These addresses are

latched during Data Writes, Erase and Lock-Block operations.

LOW-BYTE DATA BUS: Inputs data and commands during CUI write cycles.

DQ0 - DQ7 INPUT/OUTPUT Outputs array, buffer, identifier or status data in the appropriate Read mode. Floated

when the chip is de-selected or the outputs are disabled.

HIGH-BYTE DATA BUS: Inputs data during x16 Data-Write operations. Outputs

DQ8 - DQ15 INPUT/OUTPUT array, buffer or identifier data in the appropriate Read mode; not used for Status

register reads. Floated when the chip is de-selected or the outputs are disabled.

CE»0, CE »1 INPUT

RP »

INPUT

CHIP ENABLE INPUTS: Activate the device’s control logic, input buffers, decoders and

sense amplifiers. With either CE»0 or CE »1 high, the device is de-selected and power

consumption reduces to Standby levels upon completion of any current Data-Write or

Erase operations. Both CE »0, CE »1 must be low to select the device. All timing

specifications are the same for both signals. Device Selection occurs with the latter

falling edge of CE»0 or CE»1. The first rising edge of CE»0 or CE»1 disables the device.

RESET/POWER-DOWN: With RP » low, the device is reset, any current operation is

aborted and device is put into the deep power down mode. When the power is turned

on, RP » pin is turned to low in order to return the device to default configuration. When

the 3/5 » pin is switched, or when the power transition is occurred, or at the power on/off,

RP » is required to stay low in order to protect data from noise. When returning from

Deep Power-Down, a recovery time of 400 ns (VCC +5.0 V ±0.25 V) is required to allow

these circuits to power-up. When RP » goes low, any current or pending WSM

operation(s) are terminated, and the device is reset. All Status registers return to ready

(with all status flags cleared). After returning, the device is in read array mode.

OE »

INPUT

WE

INPUT

OUTPUT ENABLE: Gates device data through the output buffers when low. The

outputs float to tri-state off when OE» is high.

NOTE: CE »X overrides OE », and OE » overrides WE.

WRITE ENABLE: Controls access to the CUI, Page Buffers, Data Queue Registers

and Address Queue Latches. WE is active low, and latches both address and data

(command or array) on its rising edge.

RY »/BY »

OPEN DRAIN

OUTPUT

READY/BUSY: Indicates status of the internal WSM. When low, it indicates that the

WSM is busy performing an operation. RY»/BY » high indicates that the WSM is ready

for new operations (or WSM has completed all pending operations), or Erase is

Suspended, or the device is in deep power-down mode. This output is always active

(i.e., not floated to tri-state off when OE» or CE»0, CE»1 are high), except if a RY»/BY »

Pin Disable command is issued.

4