QL4016 Просмотр технического описания (PDF) - QuickLogic Corporation

Номер в каталоге

Компоненты Описание

производитель

QL4016 Datasheet PDF : 35 Pages

| |||

Military QuickRAM Family Data Sheet Rev. C

Symbol

tACK

tGCKP

tGCKB

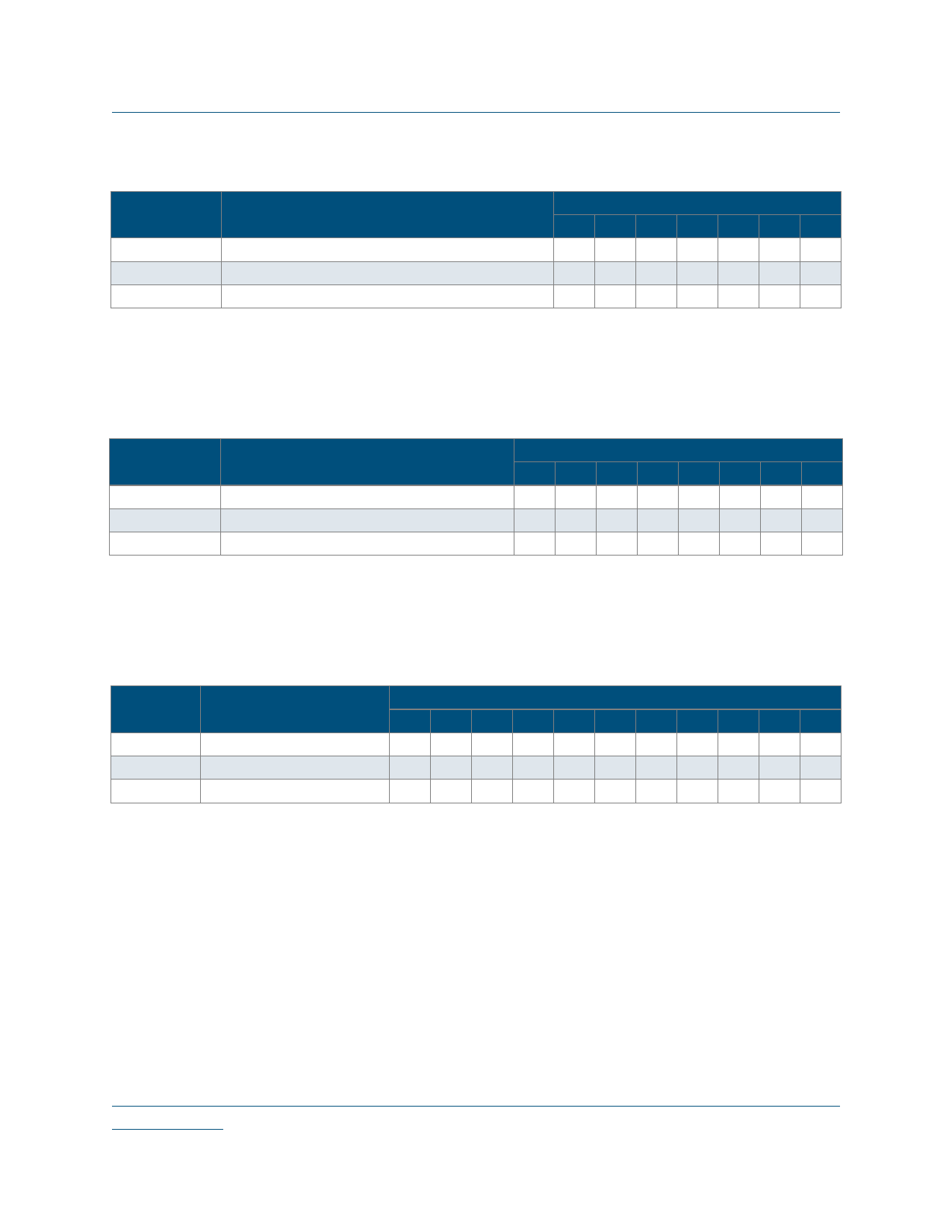

Table 11: 4016 Clock Cells

Parameter

Propagation Delays (ns) Fanouta

1 2 3 4 8 10 11

Array Clock Delay

1.2 1.2 1.3 1.3 1.5 1.6 1.7

Global Clock Pin Delay

0.7 0.7 0.7 0.7 0.7 0.7 0.7

Global Clock Buffer Delay

0.8 0.8 0.9 0.9 1.1 1.2 1.3

a. The array distributed networks consist of 40 half columns and the global distributed networks consist of 44 half columns, each driven

by an independent buffer. The number of half columns used does not affect clock buffer delay. The array clock has up to 8 loads per

half column. The global clock has up to 11 loads per half column.

Symbol

tACK

tGCKP

tGCKB

Table 12: 4036 Clock Cells

Parameter

Propagation Delays (ns) Fanouta

1 2 3 4 8 10 12 15

Array Clock Delay

1.2 1.2 1.3 1.3 1.5 1.6 1.7 1.8

Global Clock Pin Delay

0.7 0.7 0.7 0.7 0.7 0.7 0.7 0.7

Global Clock Buffer Delay

0.8 0.8 0.9 0.9 1.1 1.2 1.3 1.4

a. The array distributed networks consist of 56 half columns and the global distributed networks consist of 60 half columns, each driven

by an independent buffer. The number of half columns used does not affect clock buffer delay. The array clock has up to 12 loads

per half column. The global clock has up to 15 loads per half column.

Symbol

tACK

tGCKP

tGCKB

Table 13: 4090 Clock Cells

Parameter

Propagation Delays (ns) Fanouta

1 2 3 4 8 10 12 14 16 18 20

Array Clock Delay

1.2 1.2 1.3 1.3 1.5 1.6 1.7 1.8 1.9 2.0 2.1

Global Clock Pin Delay 0.7 0.7 0.7 0.7 0.7 0.7 0.7 0.7 0.7 0.7 0.7

Global Clock Buffer Delay 0.8 0.8 0.9 0.9 1.1 1.2 1.3 1.4 1.5 1.6 1.7

a. The array distributed networks consist of 88 half columns and the global distributed networks consist of 92 half columns, each driven

by an independent buffer. The number of half columns used does not affect clock buffer delay. The array clock has up to 18 loads

per half column. The global clock has up to 20 loads per half column.

8

•

•••

••

www.quicklogic.com

© 2007 QuickLogic Corporation