SPT9110 Просмотр технического описания (PDF) - Signal Processing Technologies

Номер в каталоге

Компоненты Описание

производитель

SPT9110 Datasheet PDF : 11 Pages

| |||

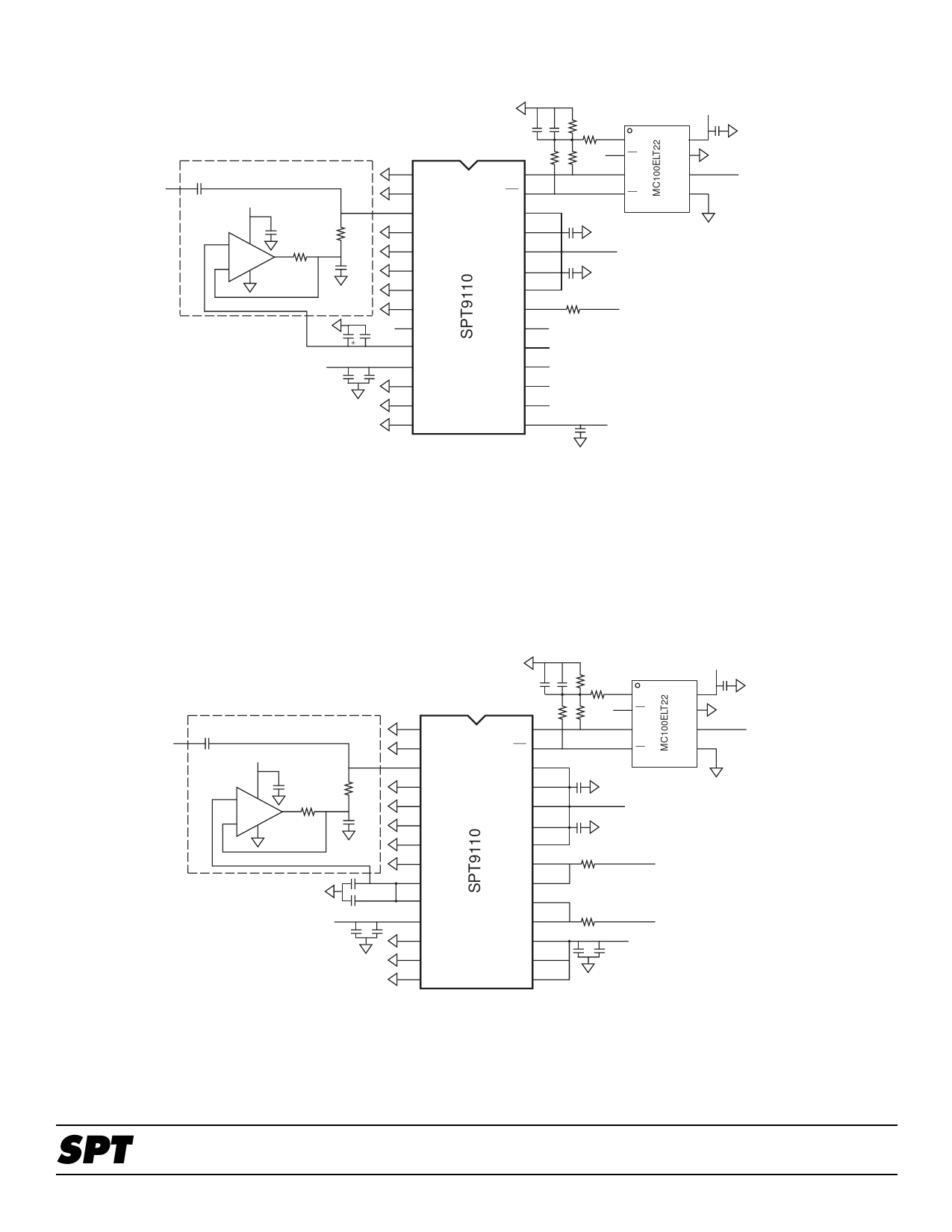

Figure 3 - Typical Interface Circuit (Single-Ended Operational Design)

Analog In

(Optional Level-Shift Circuit)

XUF (Dependent on Frequency)

A+5V

3

+

7

OP191

2-

4

0.01 µF

6

22

(+2.5 V)

50

0.1 µF

1 GND(THA)

2 GND(THA)

3 Analog IN

4 GND(SUB)

5 GND(THA)

6 GND(CAP)

7 GND(THA)

8 GND(THA)

N/C

4.7 µF

0.01 µF

A+5V

+

4.7 µF

9 REF IN

10 REF OUT

11 AVCC(Ref)

12 GND(Ref)

0.01 µF

13 GND(SUB)

14 GND(INV)

1 µF

0.01 µF

(+3.0 V)

300

+

10

50

50

CLK 28

27

CLK

AVCC(THA) 26

AVCC(THA) 25

24

AVCC(THA)

23

AVCC(THA)

AVCC(THA) 22

OUT+ 21

INV A 20

INV B 19

4.7 µF

+

0.01 µF

22

N/C

N/C

18

OUT-

N/C

AVCC(INV) 17 N/C

AVCC(INV)

AVCC(ESD)

16 N/C

15

0.01 µF

(TTL to PECL

Translator)

A+5V

1

Q0

2

Q0

3

Q1

4

Q1

VCC 8

7

DO

6

D1

5

GND

0.1 µF

TTL Clock

(Sample Clock, up to 100 MHz)

A+5V

OUT

A+5V

Notes:

1. Input signal is typically at a +2.5 V offset. The optional level-shift circuit may be eliminated if

driving from a source that already provides for this offset.

2. The device may be operated from -5 V supply on GND pins and 0 V on AVCC pins. All input and

output pins will be shifted by -5 V. The use of an ECL level may be used to drive the clock inputs.

3. VCC (ESD) is the high voltage for the ESD protection diodes and must be connected in all

applications. NOTE: It should be tied to VCC (THA), not to VCC (INV).

Figure 4 - Typical Interface Circuit (Differential Operational Design)

Analog In

(Optional Level-Shift Circuit)

XUF (Dependent on Frequency)

A+5V

3

+

7

OP191

2-

4

0.01 µF

6

22

50

0.1 µF

(+2.5 V)

+

4.7 µF

0.01 µF

A+5V

+

4.7 µF

0.01 µF

1 GND(THA)

2 GND(THA)

3 Analog IN

4 GND(SUB)

5 GND(THA)

6 GND(CAP)

7 GND(THA)

8 GND(THA)

9 REF IN

10 REF OUT

11 AVCC(Ref)

12 GND(Ref)

13 GND(SUB)

14 GND(INV)

1 µF

0.01 µF

(+3.0 V)

300

+

10

50

50

CLK 28

27

CLK

(TTL to PECL

Translator)

A+5V

1

Q0

2

Q0

3

Q1

4

Q1

VCC 8

7

DO

6

D1

5

GND

0.1 µF

TTL Clock

(Sample Clock, up to 100 MHz)

AVCC(THA) 26

AVCC(THA) 25

24

AVCC(THA)

23

AVCC(THA)

AVCC(THA) 22

4.7 µF

+

0.01 µF

A+5V

OUT+ 21

INV A 20

INV B 19

OUT+

22

(Differential Output)

18

22

OUT-

OUT-

AVCC(INV) 17

AVCC(INV) 16

15

AVCC(ESD)

0.01 µF

+

A+5V

4.7 µF

SPT

Notes:

1. Input signal is typically at a +2.5 V offset. The optional level-shift circuit may be eliminated if

driving from a source that already provides for this offset.

2. The device may be operated from -5 V supply on GND pins and 0 V on AVCC pins. All input and

output pins will be shifted by -5 V. The use of an ECL level may be used to drive the clock inputs.

3. VCC (ESD) is the high voltage for the ESD protection diodes and must be connected in all

applications. NOTE: It should be tied to VCC (THA), not to VCC (INV).

7

SPT9110

11/12/98