PCF2113AU Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

производитель

PCF2113AU Datasheet PDF : 72 Pages

| |||

Philips Semiconductors

LCD controllers/drivers

Product specification

PCF2113x

7.3 Oscillator

The on-chip oscillator provides the clock signal for the

display system. No external components are required and

the OSC pin must be connected to VDD1.

7.4 External clock

If an external clock is to be used this input is at the OSC

pin. The resulting display frame frequency is given by:

fframe = 3--f-O--0--S-7--C--2-

Only in the Power-down mode is the clock allowed to be

stopped (OSC connected to VSS), otherwise the LCD is

frozen in a DC state.

7.5 Power-on reset

The on-chip Power-on reset block initializes the chip after

power-on or power failure. This is a synchronous reset and

requires 3 oscillator cycles to be executed.

7.6 Power-down mode

The chip can be put into Power-down mode by applying an

external active HIGH level to the PD pin. In Power-down

mode all static currents are switched off (no internal

oscillator, no bias level generation and all LCD outputs are

internally connected to VSS).

During power-down, information in the RAMs and the chip

state are preserved. Instruction execution during

power-down is possible when pin OSC is externally

clocked.

7.7 Registers

The PCF2113x has two 8-bit registers, an Instruction

Register (IR) and a Data Register (DR). The Register

Select (RS) signal determines which register will be

accessed. The instruction register stores instruction codes

such as ‘display clear’, ‘cursor shift’, and address

information for the Display Data RAM (DDRAM) and

Character Generator RAM (CGRAM).The instruction

register can be written to but not read from by the system

controller.

The data register temporarily stores data to be read from

the DDRAM and CGRAM. When reading, data from the

DDRAM or CGRAM corresponding to the address in the

instruction register is written to the data register prior to

being read by the ‘read data’ instruction.

7.8 Busy flag

The busy flag indicates the internal status of the

PCF2113x. A logic 1 indicates that the chip is busy and

further instructions will not be accepted. The busy flag is

output to pin DB7 when bit RS = 0 and bit R/W = 1.

Instructions should only be written after checking that the

busy flag is at logic 0 or waiting for the required number of

cycles.

7.9 Address Counter (AC)

The address counter assigns addresses to the DDRAM

and CGRAM for reading and writing and is set by the

commands ‘set CGRAM address’ and ‘set DDRAM

address’. After a read/write operation the address counter

is automatically incremented or decremented by 1.

The address counter contents are output to the bus

(DB6 to DB0) when bit RS = 0 and bit R/W = 1.

7.10 Display Data RAM (DDRAM)

The DDRAM stores up to 80 characters of display data

represented by 8-bit character codes. RAM locations

which are not used for storing display data can be used as

general purpose RAM. The basic RAM to display

addressing scheme is shown in Fig.3. With no display shift

the characters represented by the codes in the first

24 RAM locations starting at address 00H in line 1 are

displayed. Figures 4 and 5 show the display mapping for

right and left shift respectively.

When data is written to or read from the DDRAM,

wrap-around occurs from the end of one line to the start of

the next line. When the display is shifted each line wraps

around within itself, independently of the others. Thus all

lines are shifted and wrapped around together.

The address ranges and wrap-around operations for the

various modes are shown in Table 2.

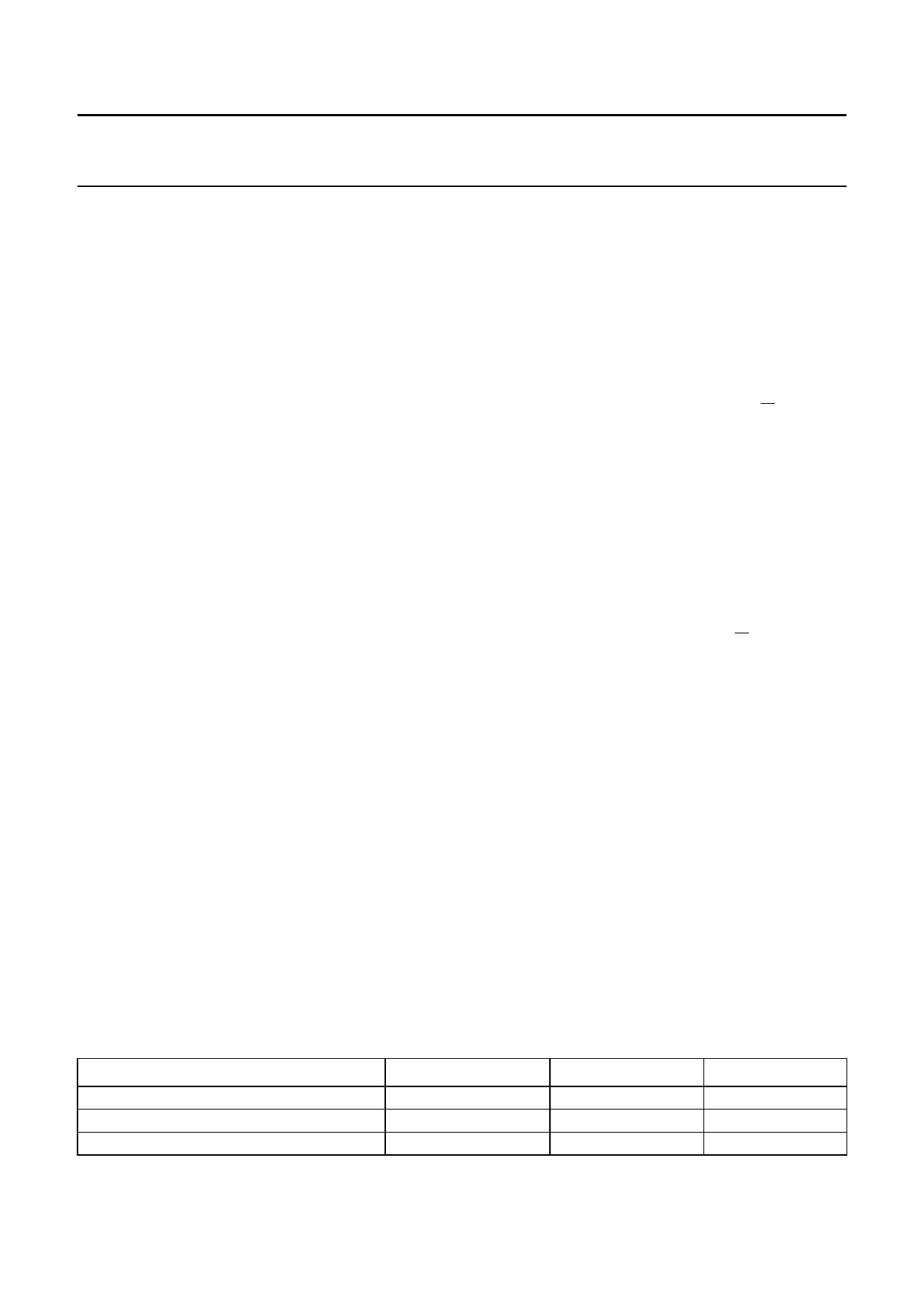

Table 2 Address space and wrap-around operation

MODE

Address space

Read/write wrap-around (moves to next line)

Display shift wrap-around (stays within line)

1 × 24

00 to 4F

4F to 00

4F to 00

2 × 12

00 to 27; 40 to 67

27 to 40; 67 to 00

27 to 00; 67 to 40

1 × 12

00 to 27

27 to 00

27 to 00

2001 Dec 19

10