MS81V06160 –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ—Ö–Ω–∏—á–µ—Å–∫–æ–≥–æ –æ–ø–∏—Å–∞–Ω–∏—è (PDF) - Oki Electric Industry

–ù–æ–º–µ—Ä –≤ –∫–∞—Ç–∞–ª–æ–≥–µ

–ö–æ–º–ø–æ–Ω–µ–Ω—Ç—ã –û–ø–∏—Å–∞–Ω–∏–µ

–ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç–µ–ª—å

MS81V06160 Datasheet PDF : 18 Pages

| |||

Semiconductor

MS81V06160

OPERATION MODE

Write Operation Cycle

The write operation is controlled by four control signals, SWCK, RSTW, WE, and IE. The write operation is

accomplished by cycling SWCK, and holding WE high after the write address pointer reset operation or RSTW.

RSTW must be performed for internal circuit initialization before write operation. WE must be low before and

after the reset cycle (tLWE + tFWD).

Each write operation, which begins after RSTW must contain at least 231 active write cycles, i.e., SWCK cycles

while WE and IE are high.

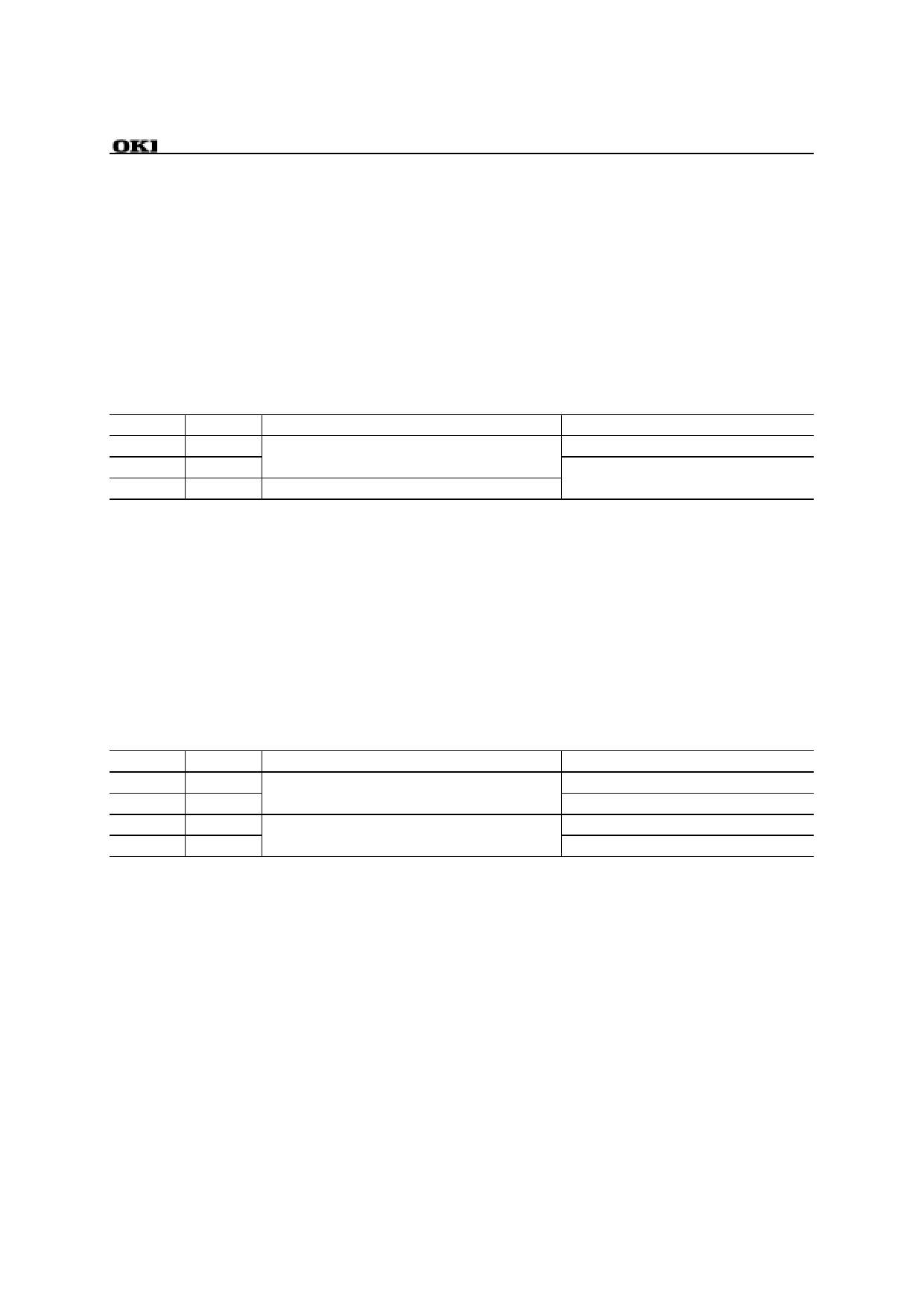

Settings of WE and IE to the operation mode of Write address pointer and Data input.

WE

IE

H

H

H

L

L

X

Internal Write address pointer

Incremented

Halted

Data input (Latency 2)

Input

Not input

X indicates "don't care"

Read Operation Cycle

The read operation is controlled by four control signals, SRCK, RSTR, RE, and OE. The read operation is

accomplished by cycling SRCK, and holding both RE and OE high after the read address pointer reset operation or

RSTR.

Each read operation, which begins after RSTR, must contain at least 231 active read cycles, i.e., SRCK cycles

while RE and OE are high. RE must be low before and after the reset cycle (tLRE + tFWD).

Settings of RE and OE to the operation mode of read address pointer and Data output.

RE

OE

H

H

H

L

L

H

L

L

Internal Read address pointer

Incremented

Halted

Data output (Latency 2)

Output

High impedance

Output

High impedance

Power-up and Initialization

On power-up, the device is designed to begin proper operation after at least 200 µs after Vcc has stabilized to a

value within the range of recommended operating conditions. After this 200 µs stabilization interval, the following

initialization sequence must be performed. Because the read and write address pointers are undefined after

power-up, a minimum of 330 dummy write operations (SWCK cycles) and read operations (SRCK cycles) must be

performed, followed by an RSTW operation and an RSTR operation, to properly initialize the write and the read

address pointer.

10/18