HI3197 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

HI3197 Datasheet PDF : 25 Pages

| |||

HI3197

AC Specifications MUX.2, SEL.A, and SEL.B Modes

CLK SIGNAL LEVEL

RESET SIGNAL LEVEL

PARAMETER

SYMBOL CONDITIONS

DIV2IN Signal Hold Time

Data Input Setup Time

Data Input Hold Time

Analog Output Pipeline Delay

Analog Output Delay

SEL. A, SEL. B MODES

tH-DIV

tS

tH

tPD (A)

tPD (B)

tDO

Maximum Conversion Rate

Clock High Pulse Width

Clock Low Pulse Width

C2 Signal Setup Time

C2 Signal Hold Time

Data Input Setup Time

Data Input Hold Time

Analog Output Pipeline Delay

Analog Output Delay

NOTE:

fC

tPW1

tPW0

tS-C2

tH-C2

tS

tH

tPD (A)

tPD (B)

tDO

2. The RESET signal is not input in MUX.2, SEL. A, or SEL. B modes.

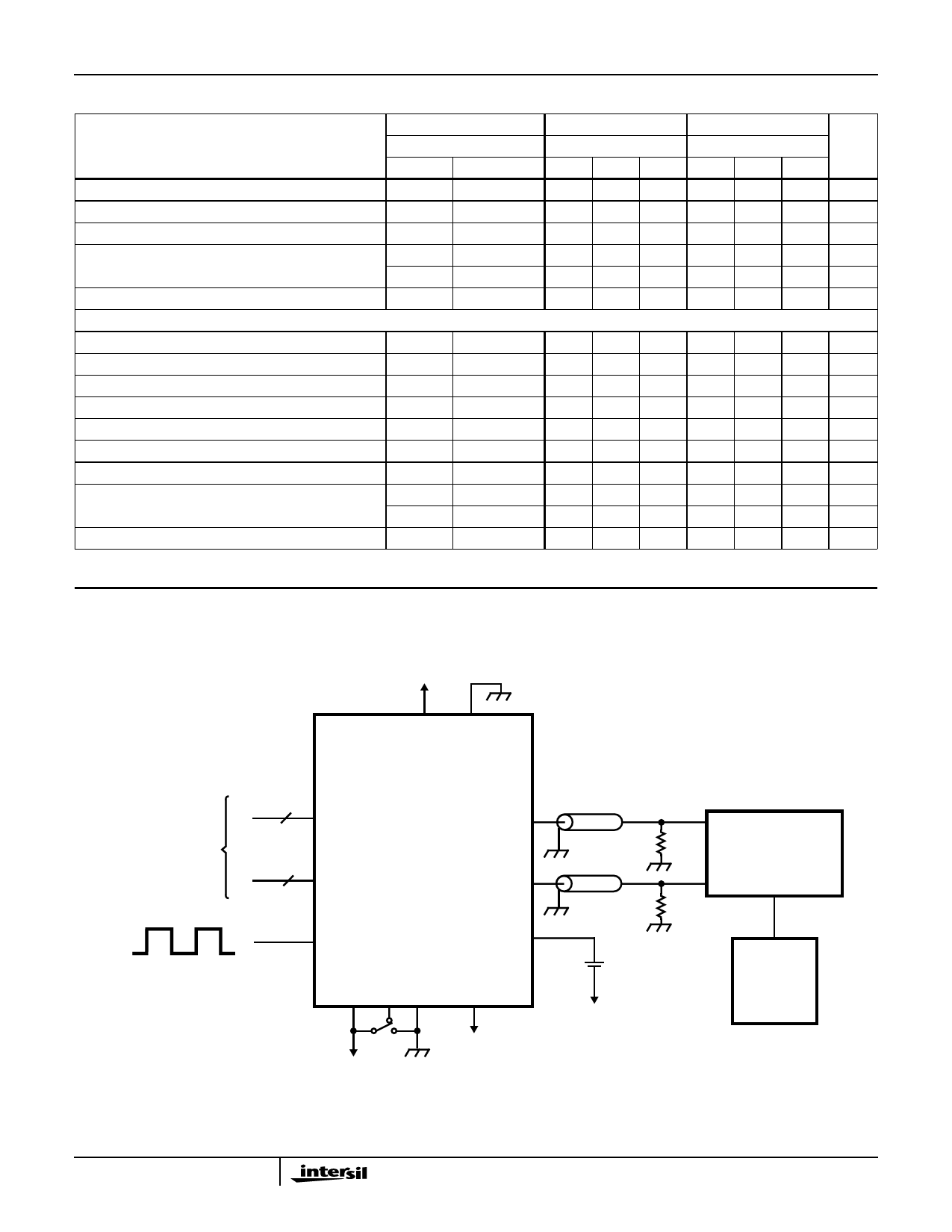

Electrical Characteristics Measurement Circuits

PECL

(NOTE 2)

MIN TYP MAX

0

-

-

1.0

-

-

5.0

-

-

-

2

-

-

3

-

5.0 5.5 6.0

125

-

-

3.5

-

-

3.5

-

-

1.0

-

-

2.5

-

-

1.0

-

-

2.0

-

-

-

1

-

-

1

-

5.0 5.5 6.0

TTL

(NOTE 2)

MIN TYP MAX

3.5

-

-

1.0

-

-

5.0

-

-

-

2

-

-

3

-

6.5 7.5 8.5

UNITS

ns

ns

ns

CLK

CLK

ns

100

-

- MSPS

4.5

-

-

ns

3.0

-

-

ns

1.0

-

-

ns

3.5

-

-

ns

1.5

-

-

ns

3.5

-

-

ns

-

1

-

CLK

-

1

-

CLK

6.5

7.5 8.5

ns

+5V

10-BIT DATA INPUT

10

DA0

TO

DA9

DB0

10

TO

DB9

DVCC1

DGND1

DVCC2

AVCC2

AVCC0

HI3197

AOUTP

AOUTN

50Ω

DVM

(DIGITAL VOLTMETER)

50Ω

CLK/T

VSET

1MHz TTL CLK

C1 C2 C3

DGND2

AGND2

937.5mV

PC

-5V

-5V

+5V

FIGURE 1. DIFFERENTIAL LINEARITY ERROR, INTEGRAL LINEARITY ERROR

10