MX7534 Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

MX7534 Datasheet PDF : 16 Pages

| |||

Microprocessor-Compatible,

14-Bit DACs

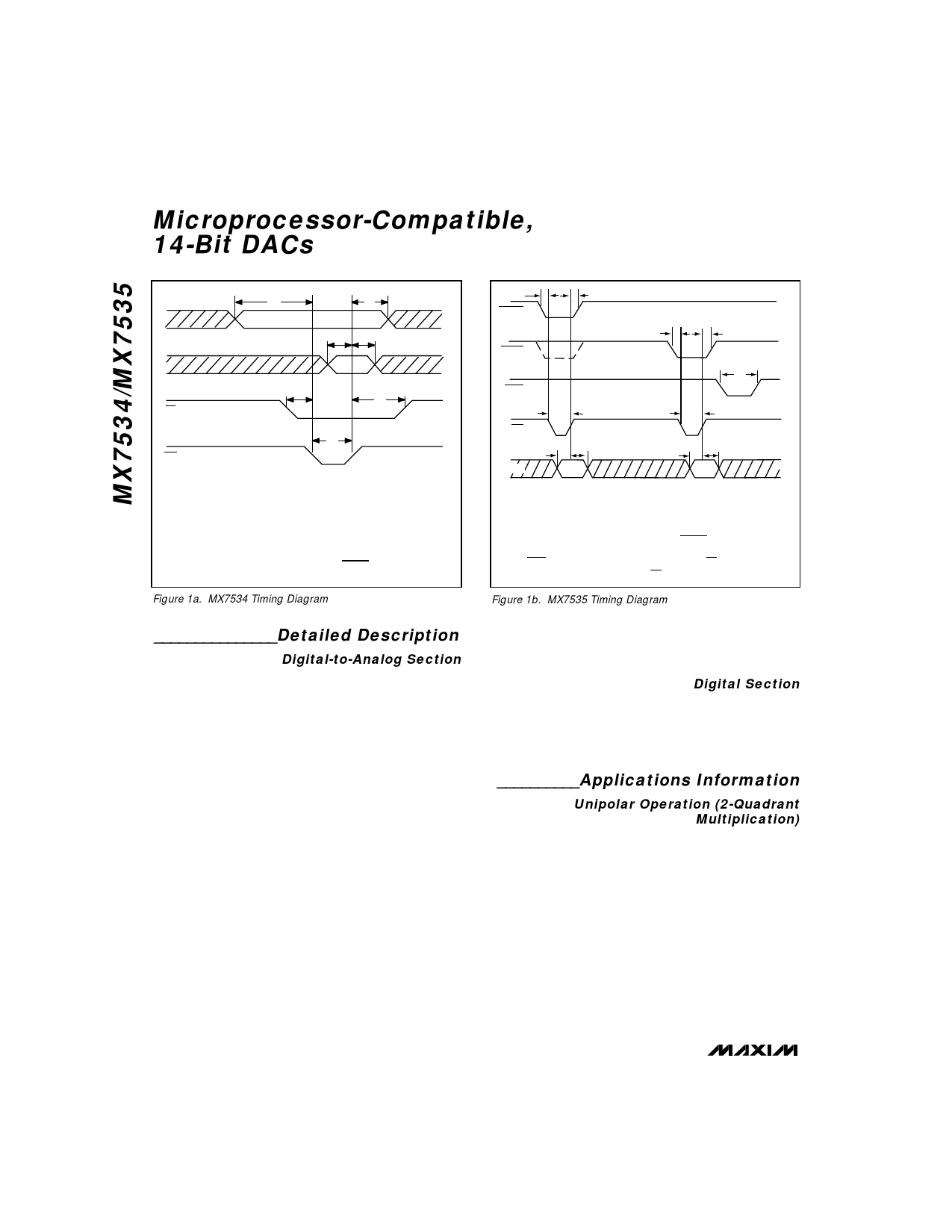

A0,A1

DATA

CS

WR

t1

t2

5V

0V

t3 t4

5V

0V

t5

t6

5V

0V

t7

5V

0V

NOTES:

1) ALL INPUT-SIGNAL RISE AND FALL TIMES ARE MEASURED FROM 10% TO 90%

OF +5V. tR = tF = 20ns.

2) TIMING MEASUREMENT REFERENCE LEVEL IS

VIH + VIL

2

Figure 1a. MX7534 Timing Diagram

t1

CSMSB

CSLSB

t2

t1

t2

5V

0V

LDAC

t3

5V

0V

WR

DATA

t4

t5 t6

t4

5V

0V

t5 t6

5V

0V

NOTES:

1) ALL INPUT-SIGNAL RISE AND FALL TIMES ARE MEASURED FROM 10% TO 90%

OF +5V. tR = tF = 20ns.

2) TIMING MEASUREMENT REFERENCE LEVEL IS

VIH + VIL

2

3) IF LDAC IS ACTIVATED PRIOR TO THE RISING EDGE OF WR, THEN IT MUST

STAY LOW FOR t3 OR LONGER AFTER WR GOES HIGH.

Figure 1b. MX7535 Timing Diagram

_______________Detailed Description

Digital-to-Analog Section

The basic MX7534/MX7535 digital-to-analog converter

(DAC) circuit consists of a laser-trimmed, thin-film,

11-bit R-2R resistor array, a 3-bit segmented resistor

array, and NMOS current switches, as shown in Figure

2. The three MSBs are decoded to drive switches A–G

of the segmented array, and the remaining bits drive

switches S0–S10 of the R-2R array.

Binary weighted currents are switched to either AGNDF

or IOUT, depending on the status of each input bit. The

R-2R ladder current is one-eighth of the total reference

input current. The remaining seven-eighths of the cur-

rent flows in the segmented resistors, dividing equally

among these seven resistors. The input resistance at

REF is constant; therefore, it can be driven by a voltage

or current source of positive or negative polarity.

The MX7534/MX7535 are optimized for unipolar output

operation (analog output from 0V to -VREF), although

bipolar operation (analog output from +VREF to -VREF) is

possible with some added external components.

Figure 3 shows the equivalent circuit for the two DACs.

COUT varies from about 90pF to 180pF, depending on

the digital code. R0 denotes the DAC’S equivalent out-

put resistance, which varies with the input code.

g(VREF,N) is the Thevenin equivalent voltage generator

due to the reference input voltage, VREF, and the trans-

fer function of the R-2R ladder, N.

Digital Section

All digital inputs are both TTL and 5V CMOS logic compat-

ible. The digital inputs are protected from electrostatic dis-

charge (ESD) with typical input currents of less than 1nA.

To minimize power-supply currents, keep digital input volt-

ages as close to 0V and 5V logic levels as possible.

__________Applications Information

Unipolar Operation (2-Quadrant

Multiplication)

Figures 4a and 4b show the circuit diagram for unipolar

binary operation. With an AC input, the circuit performs

2-quadrant multiplication. The code table for Figure 4 is

given in Table 2.

Capacitor C1 provides phase compensation and helps

prevent overshoot and ringing when high-speed op

amps are used. Note that the output polarity is the

inverse of the reference input.

6 _______________________________________________________________________________________