MT9076 Просмотр технического описания (PDF) - Zarlink Semiconductor Inc

Номер в каталоге

Компоненты Описание

производитель

MT9076 Datasheet PDF : 172 Pages

| |||

MT9076B

Data Sheet

Pin Description

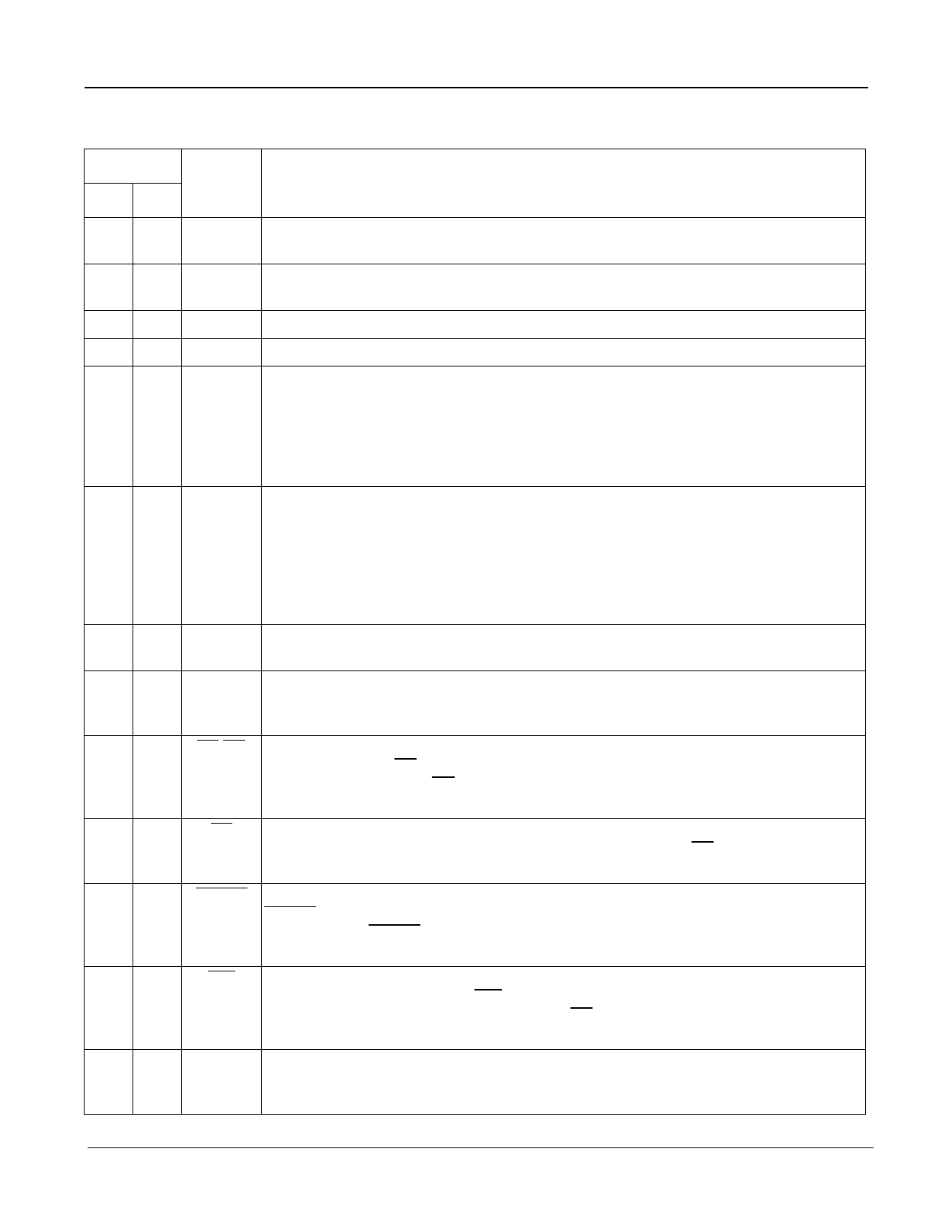

Pin #

Name

PLCC LQFP

Description

1 51 OSC1 Oscillator (3 V Input). This pin is either connected via a 20.000 MHz crystal to OSC2

where a crystal is used, or is directly driven when a 20.000 MHz. oscillator is employed.

2 52 OSC2 Oscillator (3 V Output). Connect a 20.0 MHz crystal between OSC1 and OSC2. Not

suitable for driving other devices.

3 53

VSS4 Negative Power Supply. Digital ground.

4 54

VDD4 Positive Power Supply. Digital supply (+3.3 V ± 5%).

5 55 CSTo Control ST-BUS (5 V tolerant Output). CSTo carries serial streams for CAS and CCS

respectively a 2.048 Mbit/s ST-BUS status stream which contains the 30 receive

signaling nibbles (ABCDZZZZ or ZZZZABCD). The most significant nibbles of each ST-

BUS time slot are valid and the least significant nibbles of each ST-BUS time slot are

tristated when control bit MSN (page 01H, address 1AH, bit 1) is set to 1. If MSN=0, the

position of the valid and tristated nibbles are reversed.

6 56 CSTi Control ST-BUS (5 V tolerant Input). CSTi carries serial streams for CAS and CCS

respectively a 2.048 Mbit/s ST-BUS control stream which contains the 30 transmit

signaling nibbles (ABCDXXXX or XXXXABCD) when RPSIG=0. When RPSIG=1 this

pin has no function. The most significant nibbles of each ST-BUS time slot are valid and

the least significant nibbles of each ST-BUS time slot are ignored when control bit MSN

(page 01H, address 1AH, bit 1) is set to 1. If MSN=0, the position of the valid and

ignored nibbles is reversed.

7 57 DSTo Data ST-BUS (5 V tolerant Output). A 2.048 Mbit/s serial stream which contains the

24/30 PCM(T1/E1) or data channels received on the PCM 24/30 (T1/E1) line.

8 58

DSTi

Data ST-BUS (5 V tolerant Input). A 2.048 Mbit/s serial stream which contains the

24/30 (T1/E1) PCM or data channels to be transmitted on the PCM 24/30 (T1/E1)

line.

9 59 DS/RD Data/Read Strobe (5 V tolerant Input).

In Motorola mode (DS), this input is the active low data strobe of the processor

interface. In Intel mode (RD), this input is the active low read strobe of the processor

interface.

10 63

CS Chip Select (5 V tolerant Input). This active low input enables the non-multiplexed

parallel microprocessor interface of the MT9076. When CS is set to high, the

microprocessor interface is idle and all bus I/O pins will be in a high impedance state.

11 64 RESET RESET (5 V tolerant Input). This active low input puts the MT9076 in a reset condition.

RESET should be set to high for normal operation. The MT9076 should be reset after

power-up. The RESET pin must be held low for a minimum of 1 µsec. to reset the

device properly.

12 65

IRQ Interrupt Request (5 V tolerant Output). A low on this output pin indicates that an

interrupt request is presented. IRQ is an open drain output that should be connected to

VDD through a pull-up resistor. An active low CS signal is not required for this pin to

function.

13 - 66-69 D0 - D3 Data 0 to Data 3 (5 V tolerant Three-state I/O). These signals combined with D4-D7

16

form the bidirectional data bus of the parallel processor interface (D0 is the least

significant bit).

4

Zarlink Semiconductor Inc.