MT9076B Просмотр технического описания (PDF) - Zarlink Semiconductor Inc

Номер в каталоге

Компоненты Описание

производитель

MT9076B Datasheet PDF : 172 Pages

| |||

MT9076B

T1/E1/J1 3.3 V Single Chip Transceiver

Data Sheet

Features

• Combined T1/E1/J1 framer and LIU, with PLL and

3 HDLCs

• In T1/J1 mode the LIU can recover signals

attenuated by up to 36 dB (at 772 kHz)

• In E1 mode the LIU can recover signals

attenuated by up to 40 dB (at 1.024 MHz)

• Low jitter digital PLL (intrinsic jitter < 0.02UI)

• HDLCs can be assigned to any timeslot

• Comprehensive alarm detection, performance

monitoring and error insertion functions

• 2.048 Mbit/s or 8.192 Mbit/s ST-BUS streams

• Support for Inverse Mux for ATM (IMA)

• Support for V5.1 and V5.2 Access Networks

• 3.3 V operation with 5 V tolerant inputs

• Intel or Motorola non-multiplexed 8-bit

microprocessor port

• JTAG boundary scan

June 2006

Ordering Information

MT9076BP

MT9076BB

MT9076BPR

MT9076BPR1

MT9076BB1

MT9076BP1

68 Pin PLCC

80 Pin LQFP

68 Pin PLCC

68 Pin PLCC*

80 Pin LQFP*

68 Pin PLCC*

Tubes

Trays

Tape & Reel

Tape & Reel

Trays

Tubes

*Pb Free Matte Tin

-40°C to +85°C

Applications

• T1/E1/J1 add/drop multiplexers

• Access networks

• Wireless base stations

• CO and CPE equipment interfaces

• Primary rate ISDN nodes

• Digital Cross-connect Systems (DCS)

DSTi

CSTi

Tdi

Tdo

Tms

Tclk

Trst

IRQ

D7~D0

AC4

AC0

R/W/WR

CS

DS/RD

DSTo

CSTo

TxDL TxDLCLK TxMF

TxAO TxB TxA

ST-BUS

Interface

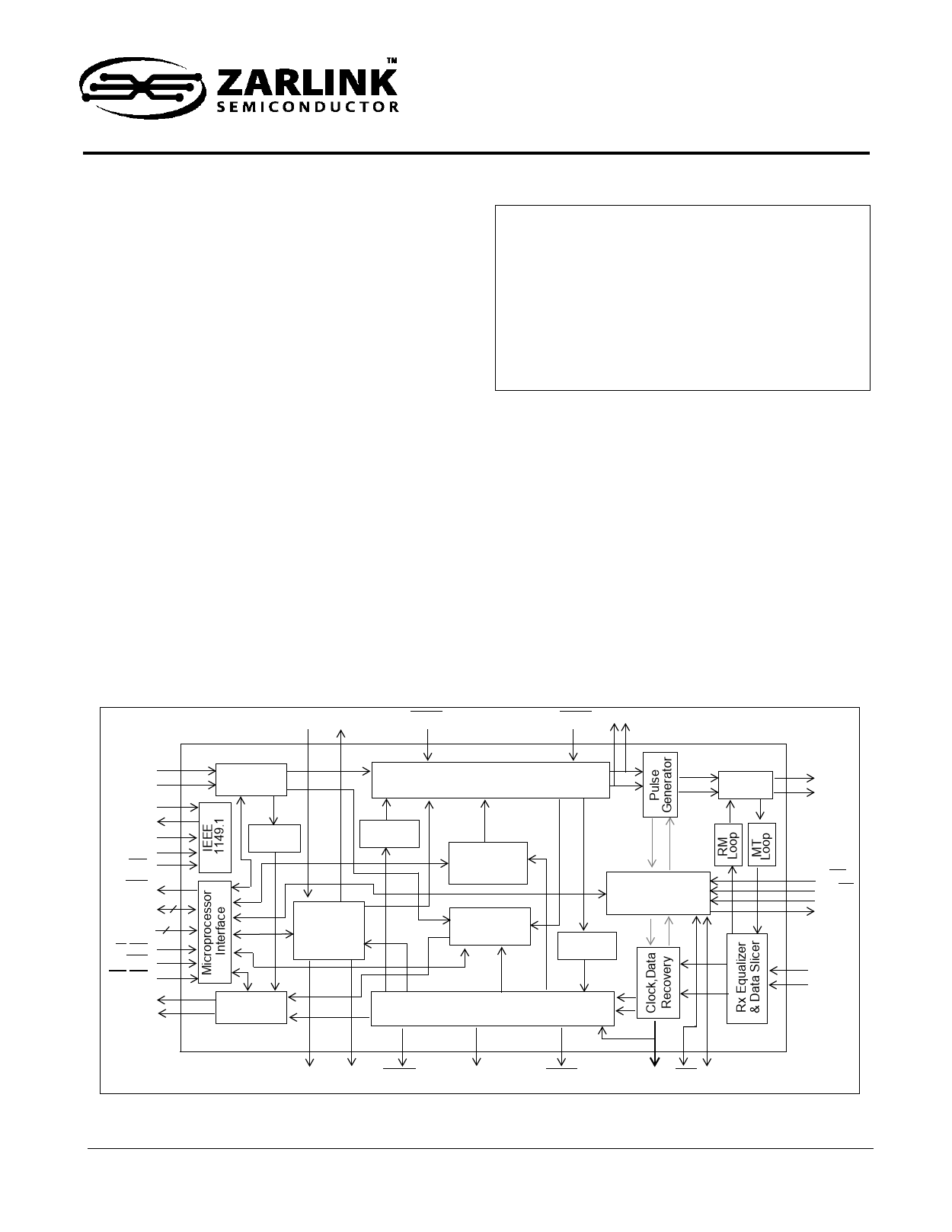

Transmit Framing, Error,

Test Signal Generation and Slip Buffer

Line

Driver

ST Loop

PL Loop

Data Link,

HDLC0

HDLC1

National

Bit Buffer

CAS

Buffer

Jitter Attenuator

& Clock Control

DG Loop

ST-BUS

Interface

Receive Framing, Performance Monitoring,

Alarm Detection, 2 Frame Slip Buffer

RxDLCLK RxDL RxMF/TxFP LOS

RxFP

Exclk F0b C4b

Figure 1 - MT9076 Functional Block

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2002-2006, Zarlink Semiconductor Inc. All Rights Reserved.

TTIP

TRING

S/FR

BS/LS

OSC1

OSC2

RTIP

RRING