MT9079 Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT9079 Datasheet PDF : 54 Pages

| |||

MT9079

don't care, CAR data D7 - D0 = page number).

Second, each page has a maximum of 16 registers

that are addressed on a read or write to a non-CAR

address (non-CAR: address AC4 = 1, AC3-AC0 =

register address, D7-D0 = data). Once a page of

memory is selected, it is only necessary to write to

the CAR when a different page is to be accessed.

See Figure 17 for timing requirements.

Communications between a serial controller and

MT9079 is a two byte operations. First, a

Command/Address byte selects the address and

operation that follows. That is, the R/W bit selects a

read or write function and A4 determines if the next

byte is a new memory page address (A4 = 0) or a

data transfer within the current memory page (A4 =

1). The second byte is either a new memory page

address (when A4 = 0) or a data byte (when A4 = 1).

This is illustrated as follows:

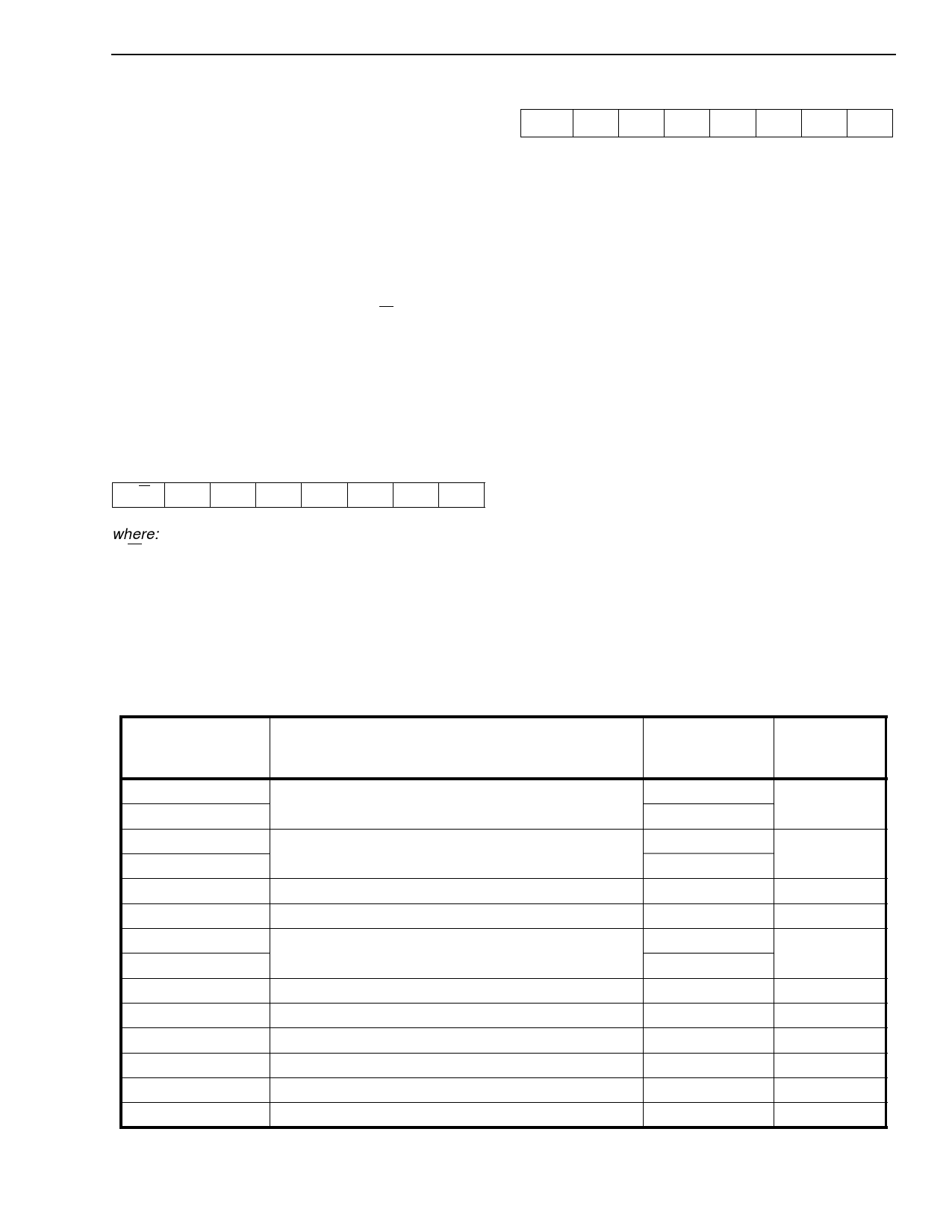

a) Command/Address byte -

R/W

X

X

A4

A3

A2

A1

A0

where:

R/W - read or write operation,

X

- no function,

A4 = 0 - new memory page address to follow,

A4 = 1 - data byte to follow, and

A3-A0 - determines the byte address.

b) Page address or data byte -

D7 D6 D5 D4 D3 D2 D1 D0

See Figures 18 and 19 for timing requirements.

Register Access and Locations

Table 2 associates the MT9079 control and status

pages with access and page descriptions, as well as

an ST-BUS stream. When ST-BUS access mode is

used, each page contains 16 registers that are

associated consecutively with the first or second 16

channels of each ST-BUS stream. That is, page 1

register locations 10000 to 11111 appear on CSTi0

time slots 0 to 15, and page 2 register locations

10000 to 11111 appear on CSTi0 time slots 16 to 31.

It should be noted that access to the transmit and

receive circular buffers is not supported in ST-BUS

mode.

Common ST-BUS Streams

There are several control and status ST-BUS

streams that are common to all modes. CSTo1

contains the received channel associated signalling

bits (e.g., CCITT R1 and R2 signalling), and when

control bit RPSIG = 0, CSTi2 is used to control the

transmit channel associated signalling. DSTi and

DSTo contain the transmit and receive voice and

digital data. Figures 4a, b and c illustrate the relative

Page Address

D7 - D0

00000001

00000010

00000011

00000100

00000101

00000110

00000111

00001000

00001001

00001010

00001011

00001100

00001101

00001110

Register Description

Master

Control

Master

Status

Per Channel Transmit Signalling

Per Channel Receive Signalling

Per Time Slot

Control

Transmit Circular Buffer Zero

Transmit Circular Buffer One

Receive Circular Buffer Zero

Receive Circular Buffer One

Transmit National Bit Buffer

Receive National Bit Buffer

Table 2 - Register Summary

Processor/

Controller

Access

R/W

R/W

R

R/W

R/W

R

R/W

R/W

R/W

R/W

R

R

R/W

R

ST-BUS

Access

CSTi0

CSTo0

CSTi2

CSTo1

CSTi1

---

---

---

---

---

---

4-245