MSM9225GA-2K Просмотр технического описания (PDF) - Oki Electric Industry

Номер в каталоге

Компоненты Описание

производитель

MSM9225GA-2K Datasheet PDF : 74 Pages

| |||

¡ Semiconductor

MSM9225

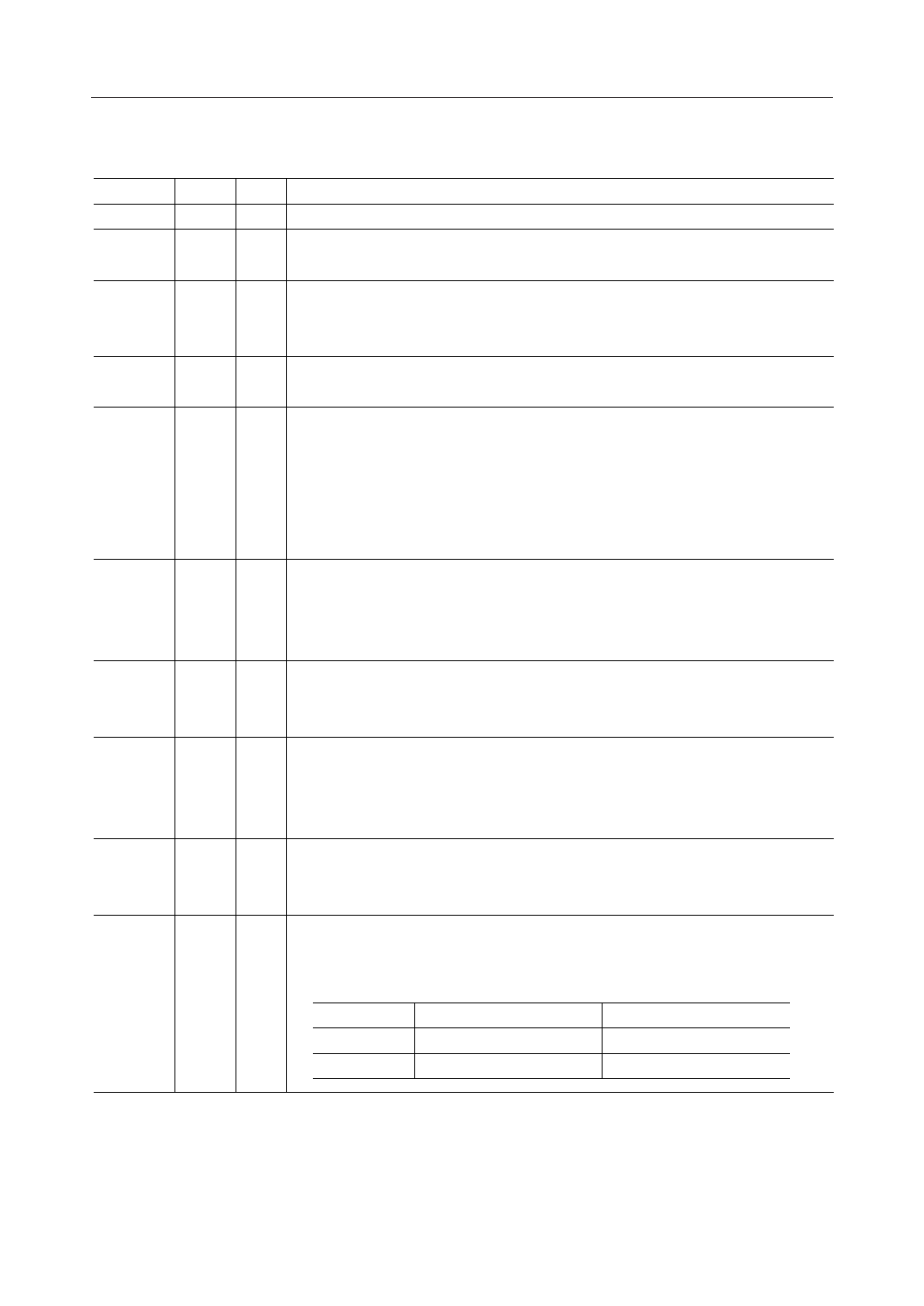

PIN DESCRIPTIONS

Symbol Pin Type

Description

CS

10

I Chip select pin. When "L", PALE, PWR, PRD/SRW, SCLK and SDO pins are valid.

41-44,

Address bus pins (when using separate buses). If used with a multiplexed bus or if

A7-0

I

1-4

used in the serial mode, fix these pins at "H" or "L" levels.

AD7-0

/D7-0

31-38

Multiplexed bus: Address/data pins

I/O Separate buses: Data pins

If used in the serial mode, fix these pins at "H" or "L" levels.

PWR

Write input pin during parallel mode. Data is captured when this pin is at a "L" level.

26

I

If used in the serial mode, fix this pin at a "H" or "L" level.

Parallel mode: Read signal pin.

When at a "L" level, data is output from the data pin.

RPD/SRW 9

Serial mode: Read/write signal pin.

I

When at a "H" level, data is output from the SDO pin.

When at a "L" level, the SDO pin is at high impedance, and data is captured beginning

with the second byte of data input from the SDI pin.

Address latch signal pin.

PALE

When at a "H" level, addresses are captured.

27

I

If used in the parallel mode and the address latch signal is unnecessary or in the

serial mode, fix this pin at a "H" or "L" level.

Serial data input pin.

SDI

7

I Addresses (1st byte) and data (beginning from the 2nd byte) are input to this pin,

LSB first. If used in the parallel mode, fix this pin at a "H" or "L" level.

Serial data output pin.

When the CS pin is at a "H" level, this pin is at high impedance. When CS is at a "L"

SDO

5

O

level, data is output from this pin LSB first.

If used in the parallel mode, fix this pin at a "H" or "L" level.

Shift clock input pin for serial data.

SCLK

8

I At the rising edge of the shift clock, SDI pin data is captured. At the falling edge, data

is output from the SDO pin.

Ready output pin.

If the microcontroller's bus cycle is fast, a signal is output to extend the bus cycle

PRDY

until the internal access is completed.

16

O

/SWAIT

Internal access in progress After completion of access

Parallel mode

"L" level output

High impedance output

Serial mode

"H" level output

"L" level output

4/73