MFRC531 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

производитель

MFRC531 Datasheet PDF : 13 Pages

| |||

Philips Semiconductors

ISO 14443 Reader IC

Short From Specification Rev. 2.0 February 2002

MF RC531

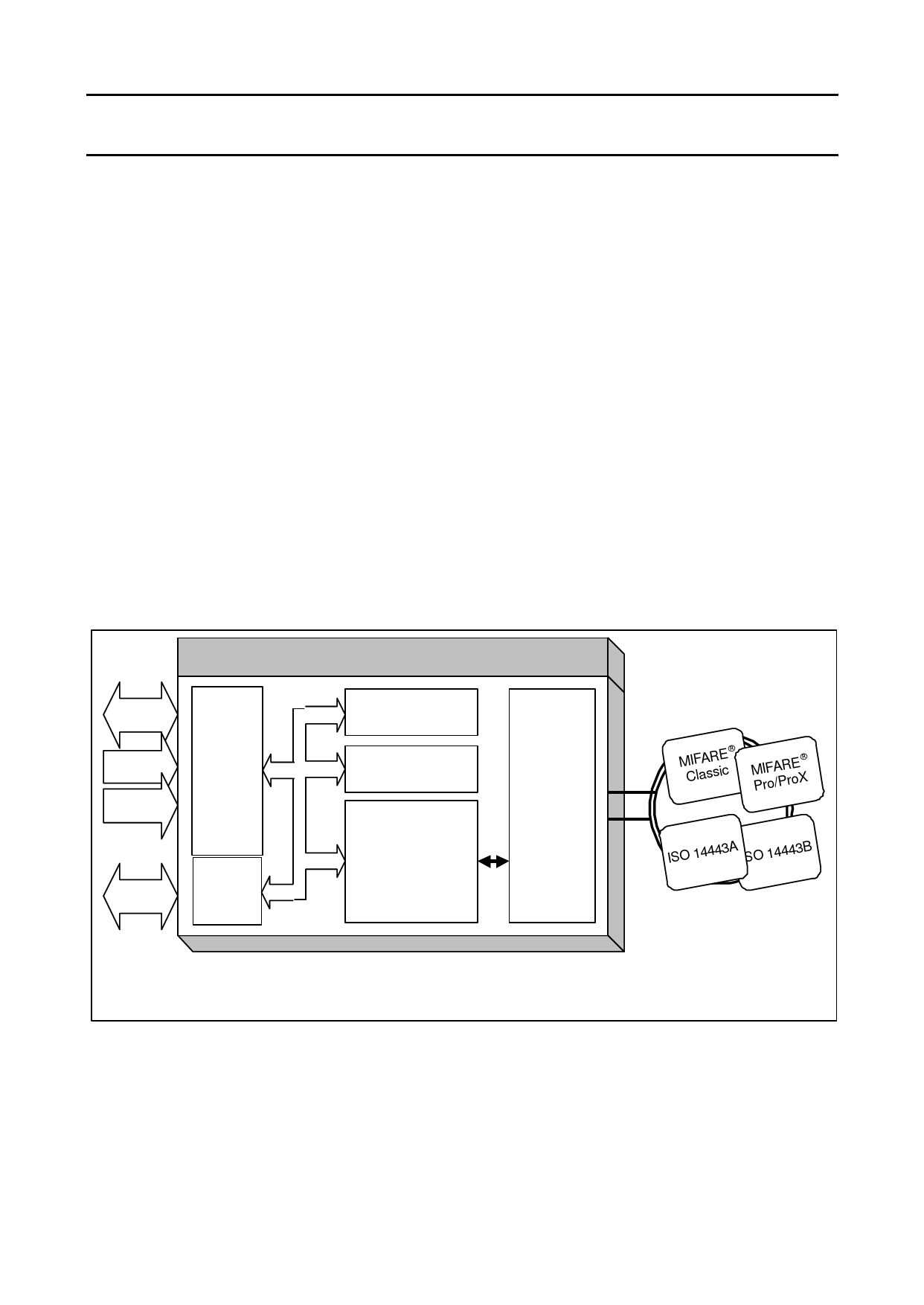

2 BLOCK DIAGRAM

The block diagram shows the main internal parts

of the MF RC531.

The parallel µController interface automatically

detects the kind of 8 bit parallel interface

connected to it. It includes a comfortable bi-

directional FIFO buffer and a configurable

interrupt output. This gives the flexibility to

connect a variety of µC, even low cost devices,

still meeting the requirements of high speed

contactless transactions.

Additionally a SPI compatible interface will be

supported. The MF RC531 acts as a slave during

the SPI communication. The SPI clock SCK has

to be generated by the master. The SPI interface

includes a comfortable bi-directional FIFO buffer.

The Data processing part performs parallel serial

conversion of the data. It supports framing

including CRC and parity generation / checking. It

operates in full transparent mode thus supporting

all layers of ISO 14443 A& B.

The status and control part allows configuration of

the device to adapt to environmental influences

and to adjust to operate with best performance.

For communication with MIFARE® Classic

products like MIFARE® Standard or MIFARE®

Light a high speed CRYPTO 1 stream cipher unit

and a secure non-volatile key memory is

implemented.

The analog circuit includes a transmitting part with

a very low impedance bridge driver output. This

allows an operating distance up to 100mm. The

receiver is able to detect and decode even very

weak responses. Due to a highly sophisticated

implementation the receiver is no longer a limiting

factor for the operating distance.

Data Bus

Addr. Bus

Control

Lines

Adress and

Data Bus

MF RC531

Status and Control

Crypto1 Security

Data Processing & Key Memory

Parallel Parallel/Serial

µController Conversion

InterfaCcReC/Parity Generation &Status and Control

wiBthuFffeIFrFOramingCCGhheeenccekkration &

Data Processing

Bit Coding and Decoding Parallel/Serial

Conversion

CRC/Parity Generation &

SPI

Check

Interface

with FIFO

Buffer

Framing Generation &

Check

Bit Coding and Decoding

Analog

Circuitry

Integrated

Demodulator,

Bit-Decoder,

Output Drivers

MCIFlaAsRsEic® MPIrFoA/PRrEoX®

ISO 14443A ISO 14443B

Figure 2-2: MF RC531 Block Diagram

4

PUBLIC