MBM29DL800BA-70PBT-SF2 –ü—Ä–ĺ—Ā–ľ–ĺ—ā—Ä —ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ–ĺ–≥–ĺ –ĺ–Ņ–ł—Ā–į–Ĺ–ł—Ź (PDF) - Fujitsu

–Ě–ĺ–ľ–Ķ—Ä –≤ –ļ–į—ā–į–Ľ–ĺ–≥–Ķ

–ö–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā—č –ě–Ņ–ł—Ā–į–Ĺ–ł–Ķ

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć

MBM29DL800BA-70PBT-SF2 Datasheet PDF : 59 Pages

| |||

MBM29DL800TA-70/-90/-12/MBM29DL800BA-70/-90/-12

s FUNCTIONAL DESCRIPTION

Simultaneous Operation

MBM29DL800TA/BA have feature, which is capability of reading data from one bank of memory while a program

or erase operation is in progress in the other bank of memory (simultaneous operation), in addition to the

conventional features (read, program, erase, erase-suspend read, and erase-suspend program). The bank

selection can be selected by bank address (A16 to A18) with zero latency.

The MBM29DL800TA/BA have two banks which contain Bank 1 (16KB, 32KB, 8KB, 8KB, 8KB, 8KB, 32KB, and

16KB) and Bank 2 (64KB √ó fourteen sectors).

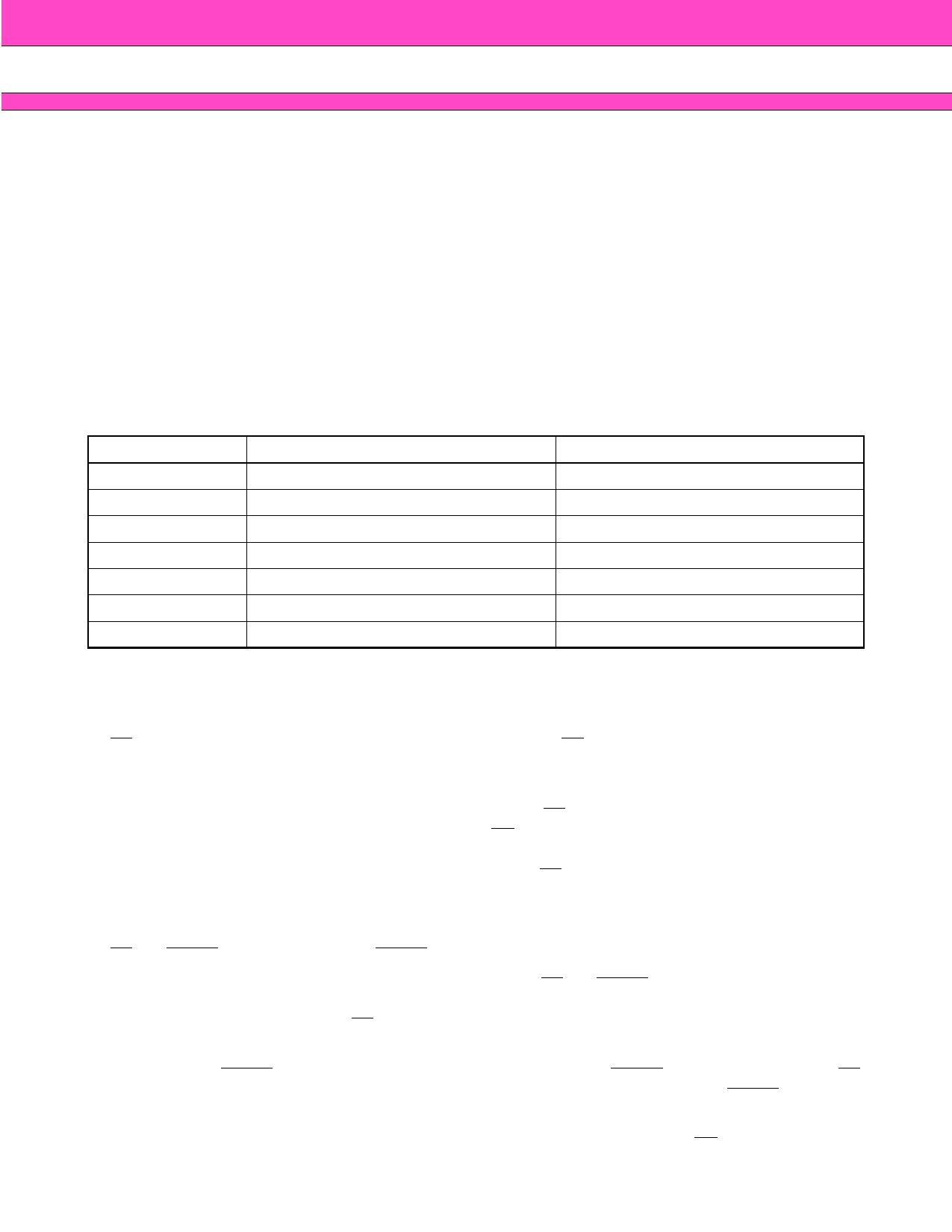

The simultaneous operation can not execute multi-function mode in the same bank. Table 4 shows combination

to be possible for simultaneous operation.

Case

1

2

3

4

5

6

7

Table 4 Simultaneous Operation

Bank 1 Status

Read mode

Read mode

Read mode

Read mode

Autoselect mode

Program mode

Erase mode *

Bank 2 Status

Read mode

Autoselect mode

Program mode

Erase mode *

Read mode

Read mode

Read mode

*: An erase operation may also be supended to read from or program to a sector not being erased.

Read Mode

The MBM29DL800TA/BA have two control functions which must be satisfied in order to obtain data at the outputs.

CE is the power control and should be used for a device selection. OE is the output control and should be used

to gate data to the output pins if a device is selected.

Address access time (tACC) is equal to the delay from stable addresses to valid output data. The chip enable

access time (tCE) is the delay from stable addresses and stable CE to valid data at the output pins. The output

enable access time is the delay from the falling edge of OE to valid data at the output pins. (Assuming the

addresses have been stable for at least tACC-tOE time.) When reading out a data without changing addresses after

power-up, it is necessary to input hardware reset or to change CE pin from ‚ÄúH‚ÄĚ or ‚ÄúL‚ÄĚ

Standby Mode

There are two ways to implement the standby mode on the MBM29DL800TA/BA devices, one using both the

CE and RESET pins; the other via the RESET pin only.

When using both pins, a CMOS standby mode is achieved with CE and RESET inputs both held at VCC ¬Ī 0.3 V.

Under this condition the current consumed is less than 5 ¬ĶA max. During Embedded Algorithm operation, VCC

active current (ICC2) is required even CE = ‚ÄúH‚ÄĚ. The device can be read with standard access time (tCE) from either

of these standby modes.

When using the RESET pin only, a CMOS standby mode is achieved with RESET input held at VSS ¬Ī 0.3 V (CE

= ‚ÄúH‚ÄĚ or ‚ÄúL‚ÄĚ). Under this condition the current is consumed is less than 5 ¬ĶA max. Once the RESET pin is taken

high, the device requires tRH of wake up time before outputs are valid for read access.

In the standby mode the outputs are in the high impedance state, independent of the OE input.

11