MAX5580A(2008) Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

MAX5580A

(Rev.:2008)

(Rev.:2008)

MAX5580A Datasheet PDF : 34 Pages

| |||

Buffered, Fast-Settling, Quad,

12-/10-/8-Bit, Voltage-Output DACs

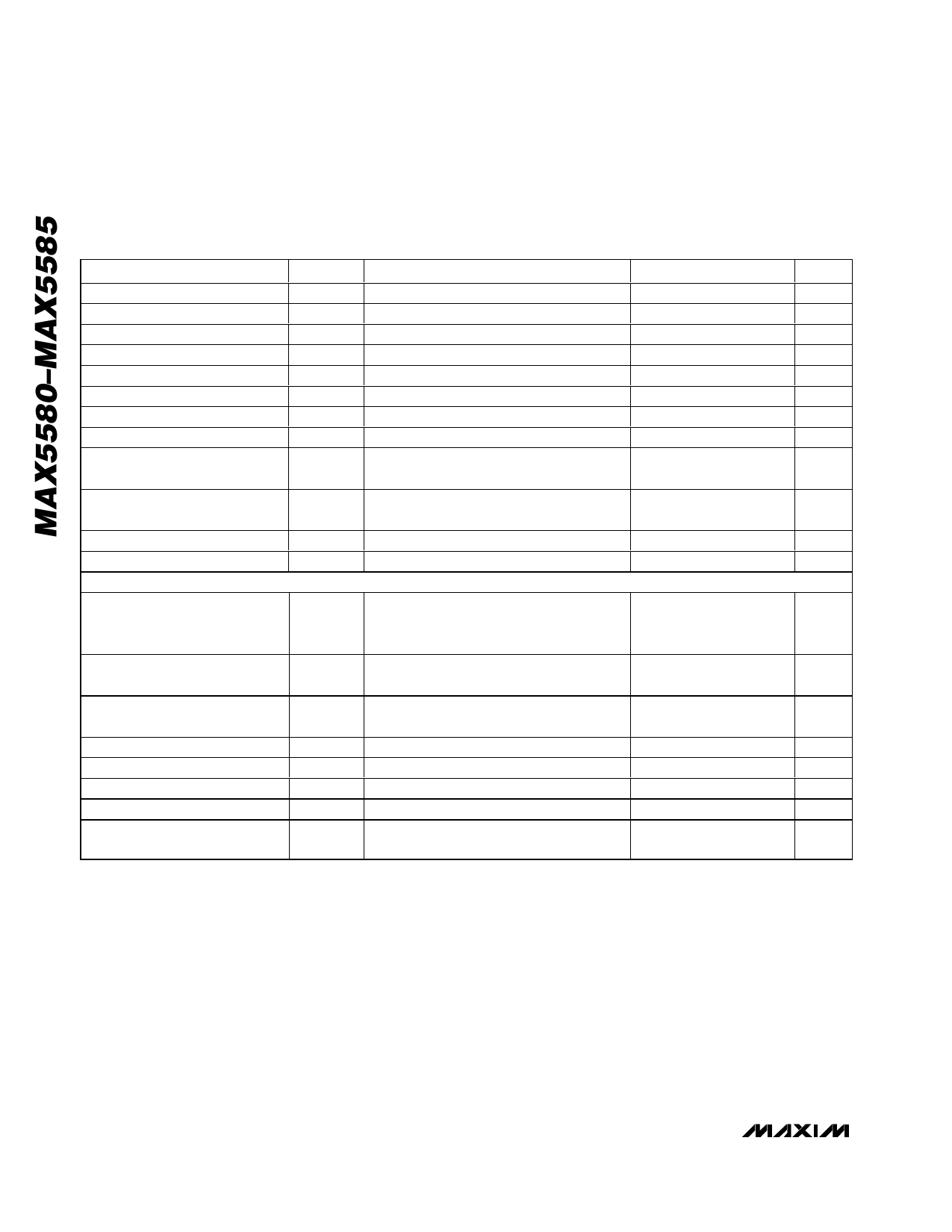

TIMING CHARACTERISTICS—DSP Mode Disabled (3V, 3.3V, 5V Logic) (Figure 1)

(DVDD = 2.7V to 5.25V, AGND = DGND = 0, TA = TMIN to TMAX, unless otherwise noted.)

PARAMETER

SCLK Frequency

SCLK Pulse-Width High

SCLK Pulse-Width Low

CS Fall to SCLK Rise Setup Time

SCLK Rise to CS Rise Hold Time

SCLK Rise to CS Fall Setup Time

DIN to SCLK Rise Setup Time

DIN to SCLK Rise Hold Time

SCLK Rise to DOUTDC1 Valid

Propagation Delay

SYMBOL

fSCLK

tCH

tCL

tCSS

tCSH

tCS0

tDS

tDH

CONDITIONS

2.7V < DVDD < 5.25V

(Note 7)

(Note 7)

tDO1 CL = 20pF, UPIO_ = DOUTDC1 mode

MIN TYP MAX

20

20

20

10

5

10

12

5

30

SCLK Fall to DOUT_ Valid

Propagation Delay

tDO2

CL = 20pF, UPIO_ = DOUTDC0 or DOUTRB

mode

30

CS Rise to SCLK Rise Hold Time

tCS1 MICROWIRE and SPI modes 0 and 3

10

CS Pulse-Width High

tCSW

45

UPIO_ TIMING CHARACTERISTICS

DOUT Tri-State Time when Exiting

DOUTDC0, DOUTDC1, and UPIO

Modes

tDOZ

CL = 20pF, from end of write cycle to UPIO_

in high impedance

100

DOUTRB Tri-State Time from CS

Rise

tDRBZ

CL = 20pF, from rising edge of CS to UPIO_

in high impedance

20

DOUTRB Tri-State Enable Time

from 8th SCLK Rise

tZEN

CL = 20pF, from 8th rising edge of SCLK to

UPIO_ driven out of tri-state

0

LDAC Pulse-Width Low

tLDL Figure 5

20

LDAC Effective Delay

tLDS Figure 6

100

CLR, MID, SET Pulse-Width Low

tCMS Figure 5

20

GPO Output Settling Time

tGP

Figure 6

100

GPO Output High-Impedance

Time

tGPZ

100

UNITS

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

6 _______________________________________________________________________________________