M88 Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

производитель

M88 Datasheet PDF : 7 Pages

| |||

M88 FAMILY

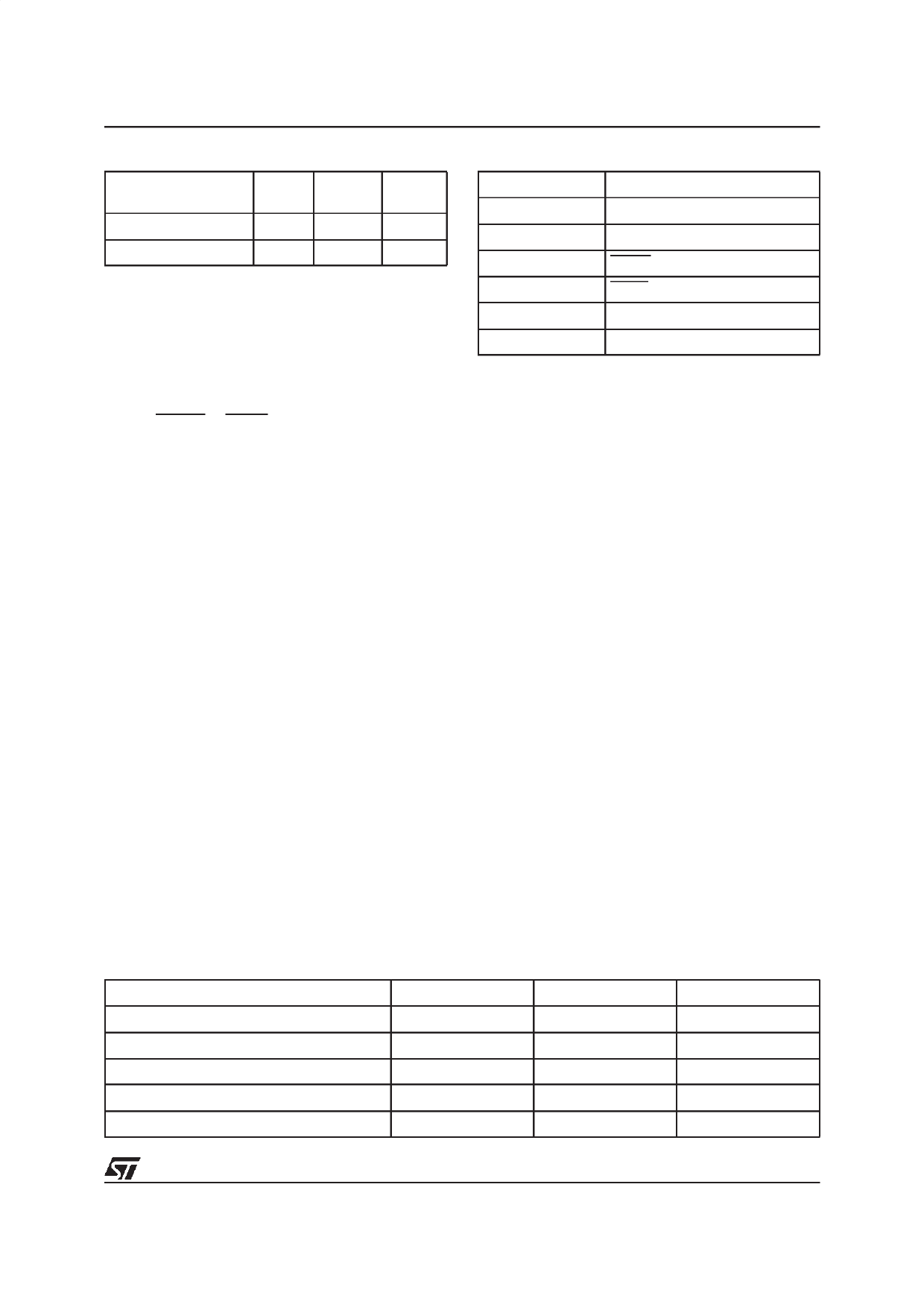

Table 3. PLD I/O

Name

Inpu ts

Outp uts

Produ ct

Terms

Decode PLD (DPLD) 73

17

42

Complex PLD (CPLD) 73

19

140

JTAG Port

In-System Programming (ISP) can be performed

through the JTAG signals on Port C. This serial

interface allows complete programming of the

entire FLASH+PSD device. A blank device can be

completely programmed for the first time after it is

soldered to the board. The JTAG signals (TMS,

TCK, TSTAT, TERR, TDI, TDO) can be

multiplexed with other functions on Port C. Table 4

indicates the JTAG pin assignments. Four-pin

JTAG is also fully supported.

In-System Programming (ISP)

Using the JTAG signals on Port C, the entire

FLASH+PSD device can be programmed or

erased without the use of the MCU. The primary

Flash memory can also be programmed in-system

by the MCU executing the programming

algorithms out of the secondary memory, or

SRAM. The secondary memory can be

programmed the same way by executing out of the

primary Flash memory. The PLD or other

FLASH+PSD Configuration blocks can be

programmed through the JTAG port or a device

insertion programmer. Table 5 indicates which

programming methods can program different

functional blocks of the FLASH+PSD.

Power Management Unit (PMU)

The Power Management Unit (PMU) gives the

user control of the power consumption on selected

functional blocks based on system requirements.

The PMU includes an Automatic Power-down

(APD) Unit that turns off device functions during

MCU inactivity. The APD Unit has a Power-down

mode that helps reduce power consumption.

The FLASH+PSD also has some bits that are

configured at run-time by the MCU to reduce

Table 4. JTAG SIgnals on Port C

Port C Pins

JTAG Signal

PC0

TMS

PC1

TCK

PC3

TSTAT

PC4

TERR

PC5

TDI

PC6

TDO

power consumption of the CPLD. The Turbo bit in

the PMMR0 register can be reset to 0 and the

CPLD latches its outputs and goes to sleep until

the next transition on its inputs.

Additionally, bits in the PMMR2 register can be set

by the MCU to block signals from entering the

CPLD to reduce power consumption. Please see

the full data sheet for more details.

SECURITY AND NVM SECTOR PROTECTION

A security bit in the Protection Register enables

the software project, coded in the FLASH+PSD, to

be locked up. This bit is only accessible by the

system designer from the JTAG serial port, or from

a parallel insertion programmer. It cannot be

accessed from the MCU. The only way a security

bit can be cleared is to erase the entire chip.

The contents of the sectors of the primary and

secondary NVM blocks can be protected using bits

in the Protection Registers. These bits are

accessible from the MCU in the application code,

or from a programmer during the set-up

procedure.

Table 5. Methods of Programming Different Functional Blocks of the FLASH+PSD

Functional Block

JTAG Programming Device Programmer

IAP

Primary Flash Memory

Yes

Yes

Yes

Secondary EEPROM or Flash memory

Yes

Yes

Yes

PLD Array (DPLD and CPLD)

Yes

Yes

No

FLASH+PSD Configuration

Yes

Yes

No

OTP Row

No

Yes

Yes

5/7