M59DR016 Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

производитель

M59DR016 Datasheet PDF : 37 Pages

| |||

M59DR016C, M59DR016D

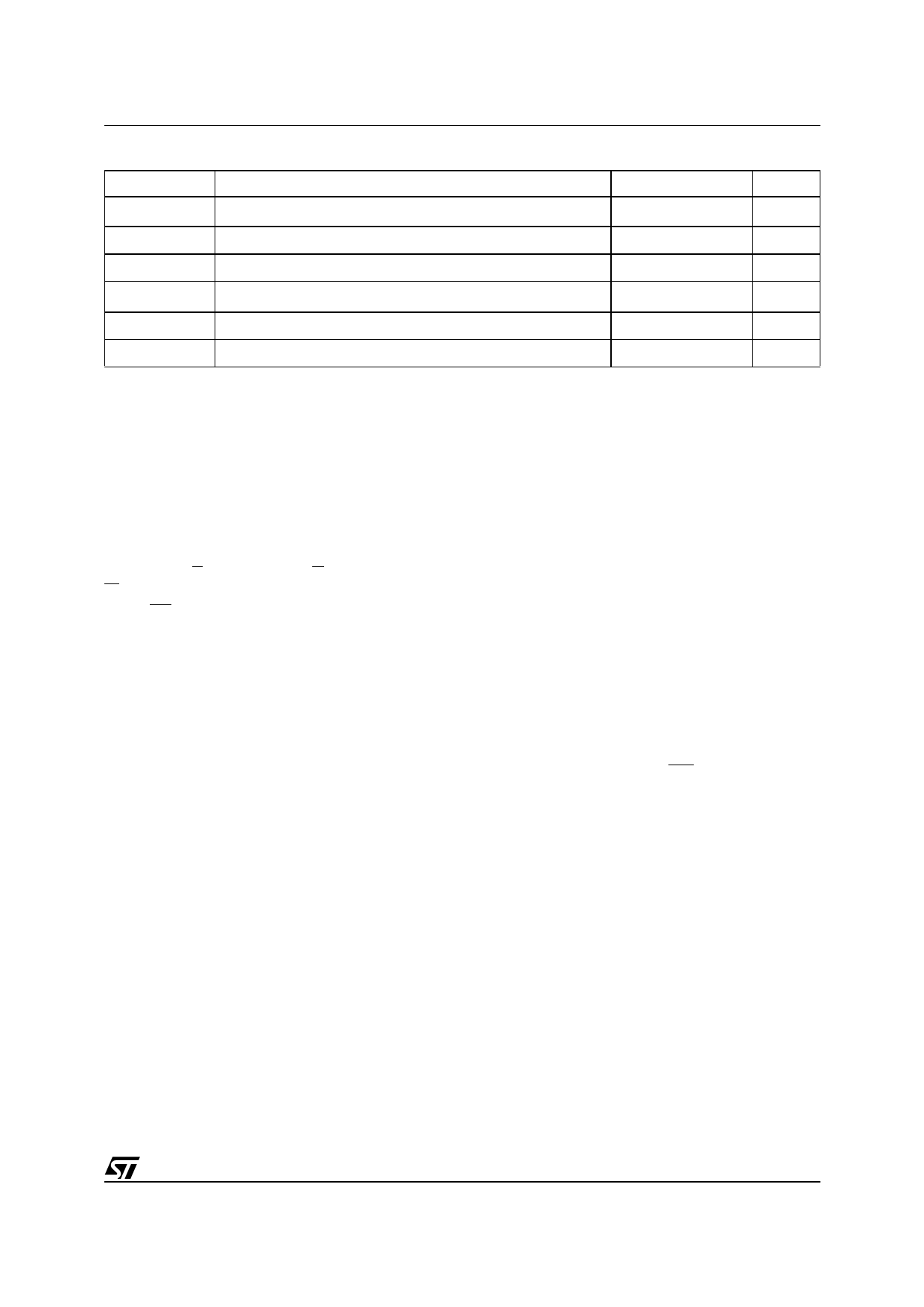

Table 2. Absolute Maximum Ratings (1)

Symbol

Parameter

Value

Unit

TA

Ambient Operating Temperature (2)

–40 to 85

°C

TBIAS

Temperature Under Bias

–40 to 125

°C

TSTG

Storage Temperature

–55 to 155

°C

VIO (3)

Input or Output Voltage

–0.5 to VDDQ+0.5

V

VDD, VDDQ Supply Voltage

–0.5 to 2.7

V

VPP

Program Voltage

–0.5 to 13

V

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may

cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions

above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating condi-

tions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant qual-

ity documents.

2. Depends on range.

3. Minimum Voltage may undershoot to –2V during transition and for less than 20ns.

Organization

The M59DR016 is organized as 1Mb x16 bits. A0-

A19 are the address lines, DQ0-DQ15 are the

Data Input/Output. Memory control is provided by

Chip Enable E, Output Enable G and Write Enable

W inputs.

Reset RP is used to reset all the memory circuitry

and to set the chip in power down mode if this

function is enabled by a proper setting of the Con-

figuration Register. Erase and Program operations

are controlled by an internal Program/Erase Con-

troller (P/E.C.). Status Register data output on

DQ7 provides a Data Polling signal, DQ6 and DQ2

provide Toggle signals and DQ5 provides error bit

to indicate the state of the P/E.C operations.

Memory Blocks

The device features asymmetrically blocked archi-

tecture. M59DR016 has an array of 39 blocks and

is divided into two banks A and B, providing Dual

Bank operations. While programming or erasing in

Bank A, read operations are possible into Bank B

or vice versa. The memory also features an erase

suspend allowing to read or program in another

block within the same bank. Once suspended the

erase can be resumed. The Bank Size and Sector-

ization are summarized in Table 7. Parameter

Blocks are located at the top of the memory ad-

dress space for the M59DR016C, and at the bot-

tom for the M59DR016D. The memory maps are

shown in Tables 3, 4, 5 and 6.

The Program and Erase operations are managed

automatically by the P/E.C. Block protection

against Program or Erase provides additional data

security. All blocks are protected at Power Up. In-

structions are provided to protect or unprotect any

block in the application. A second register locks

the protection status while WP is low (see Block

Locking description). The Reset command does

not affect the configuration of unprotected blocks

and the Configuration Register status.

3/37