LXT300Z Просмотр технического описания (PDF) - Level One

Номер в каталоге

Компоненты Описание

производитель

LXT300Z Datasheet PDF : 20 Pages

| |||

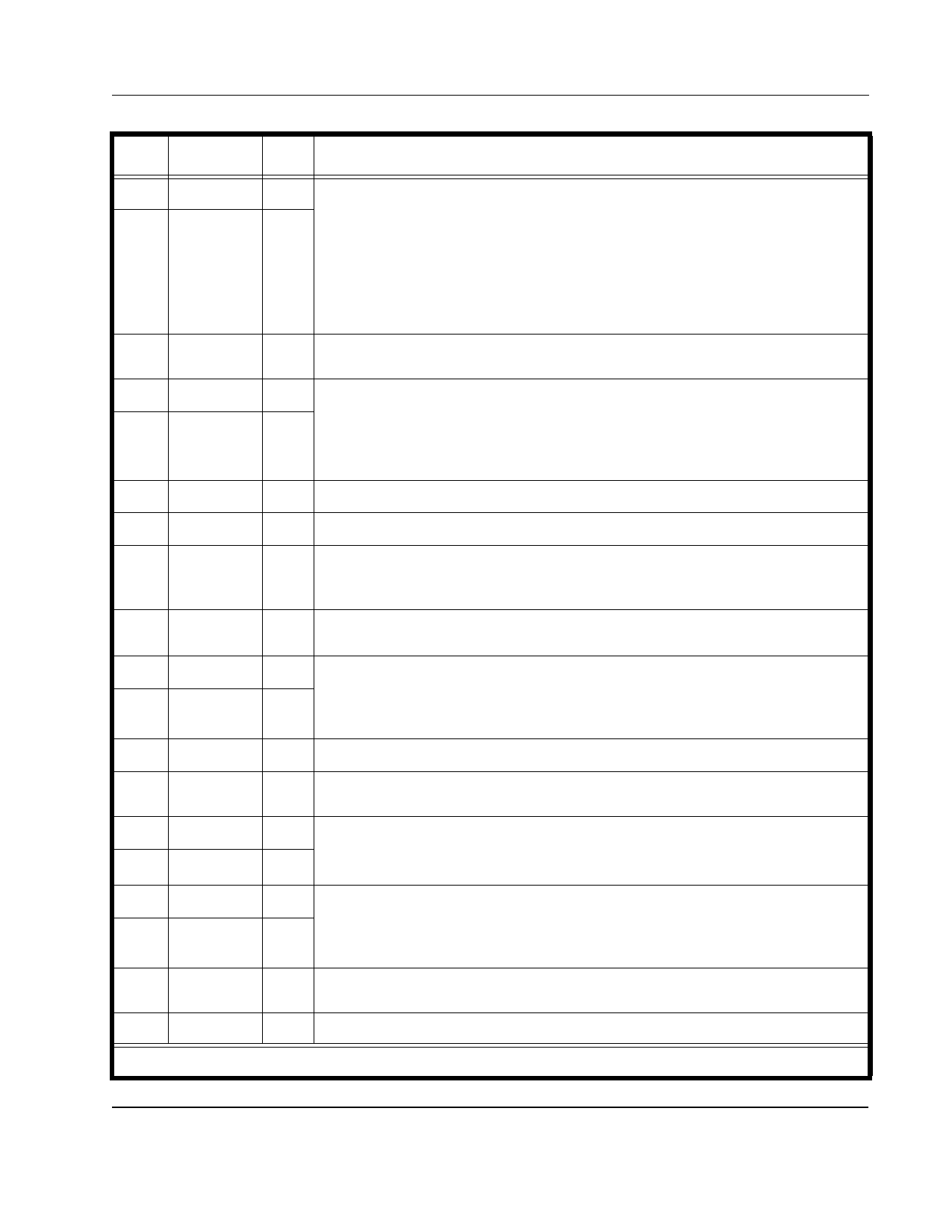

3LQ $VVLJQPHQWV ÷ 6LJQDO 'HVFULSWLRQV

7DEOH ìã 3LQ 'HVFULSWLRQV ¤ FRQWLQXHG

3LQ ú

6\P

,î2ì

'HVFULSWLRQ

ç

51(*

'2 5HFHLYH 1HJDWLYH 'DWDâ 5HFHLYH 3RVLWLYH 'DWDï Received data outputs. A signal on

RNEG corresponds to receipt of a negative pulse on RTIP and RRING. A signal on

æ

5326

'2 RPOS corresponds to receipt of a positive pulse on RTIP and RRING. RNEG and

RPOS outputs are Non-Return-to-Zero (NRZ). Both outputs are stable and valid on the

rising edge of RCLK.

LXT300Z only: In the Host Mode, CLKE determines the clock edge at which these out-

puts are stable and valid. In the Hardware Mode both outputs are stable and valid on

the rising edge of RCLK.

å

5&/.

'2 5HFRYHUHG &ORFNï This is the clock recovered from the signal received at RTIP and

RRING.

ä

;7$/,1 $, &U\VWDO ,QSXWâ &U\VWDO 2XWSXW õ/;7êíí=ôï An external crystal operating at four

times the bit rate (6.176 MHz for DSX-1, 8.192 MHz for E1 applications with an 18.7

ìí ;7$/287 $2 pF load) is required to enable the jitter attenuation function of the LXT300Z. These

pins may also be used to disable the jitter attenuator by connecting the XTALIN pin to

the positive supply through a resistor, and floating the XTALOUT pin.

ä

57

$, 5HFHLYH 7HUPLQDWLRQ õ/;7êíì=ôï &RQQHFW WR 59ò WKURXJK D ì N Ω UHVLVWRUï

ìí

1î&

¤ 1R &RQQHFWLRQ õ/;7êíì=ôï

ìì

'30

'2 'ULYHU 3HUIRUPDQFH 0RQLWRUï DPM goes High when the transmit monitor loop

(MTIP and MRING) does not detect a signal for 63 ±2 clock periods. DPM remains

High until a signal is detected.

ìë

/26

'2 /RVV RI 6LJQDOï LOS goes High when 175 consecutive spaces have been detected.

LOS returns Low when a mark is detected.

ìê

77,3

$2 7UDQVPLW 7LSâ 7UDQVPLW 5LQJï Differential Driver Outputs. These outputs are

designed to drive a 25 Ω load. The transmitter will drive 100 Ω shielded twisted-pair

ìç

75,1* $2 cable through a 1:2 step-up transformer without additional components. To drive

75 Ω coaxial cable, two 2.2 Ω resistors are required in series with the transformer.

ìé

7*1'

6 7UDQVPLW *URXQGï *URXQG UHWXUQ IRU WKH WUDQVPLW GULYHUV SRZHU VXSSO\ 79òï

ìè

79ò

6 7UDQVPLW 3RZHU 6XSSO\ï òè 9'& SRZHU VXSSO\ LQSXW IRU WKH WUDQVPLW GULYHUVï 79ò

PXVW QRW YDU\ IURP 59ò E\ PRUH WKDQ ‘íïê 9ï

ìæ

07,3

$, 0RQLWRU 7LSâ 0RQLWRU 5LQJï 7KHVH SLQV DUH XVHG WR PRQLWRU WKH WLS DQG ULQJ WUDQVPLW

RXWSXWVï 7KH WUDQVFHLYHU FDQ EH FRQQHFWHG WR PRQLWRU LWV RZQ RXWSXW RU WKH RXWSXW RI

ìå

05,1*

$, DQRWKHU /;7êíí= RU /;7êíì= RQ WKH ERDUGï

ìä

57,3

$, 5HFHLYH 7LSâ 5HFHLYH 5LQJï The AMI signal received from the line is applied at these

pins. A center-tapped, center-grounded, 2:1 step-up transformer is required on these

ëí

55,1*

$, pins. Data and clock from the signal applied at these pins are recovered and output on

the RPOS/RNEG and RCLK pins.

ëì

59ò

6 5HFHLYH 3RZHU 6XSSO\ï òè 9'& SRZHU VXSSO\ IRU DOO FLUFXLWV H[FHSW WKH WUDQVPLW GULYð

HUVï õ7UDQVPLW GULYHUV DUH VXSSOLHG E\ 79òïô

ëë

5*1'

6 5HFHLYH *URXQGï *URXQG UHWXUQ IRU SRZHU VXSSO\ 59òï

ìï (QWULHV LQ ,î2 FROXPQ DUHã ', 'LJLWDO ,QSXWâ '2 'LJLWDO 2XWSXWâ $, $QDORJ ,QSXWâ $2 $QDORJ 2XWSXWâ 6 6XSSO\ï

L1

ëðê