UPD3729D –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ—Ö–Ω–∏—á–µ—Å–∫–æ–≥–æ –æ–ø–∏—Å–∞–Ω–∏—è (PDF) - NEC => Renesas Technology

–ù–æ–º–µ—Ä –≤ –∫–∞—Ç–∞–ª–æ–≥–µ

–ö–æ–º–ø–æ–Ω–µ–Ω—Ç—ã –û–ø–∏—Å–∞–Ω–∏–µ

–ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç–µ–ª—å

UPD3729D Datasheet PDF : 20 Pages

| |||

µPD3729

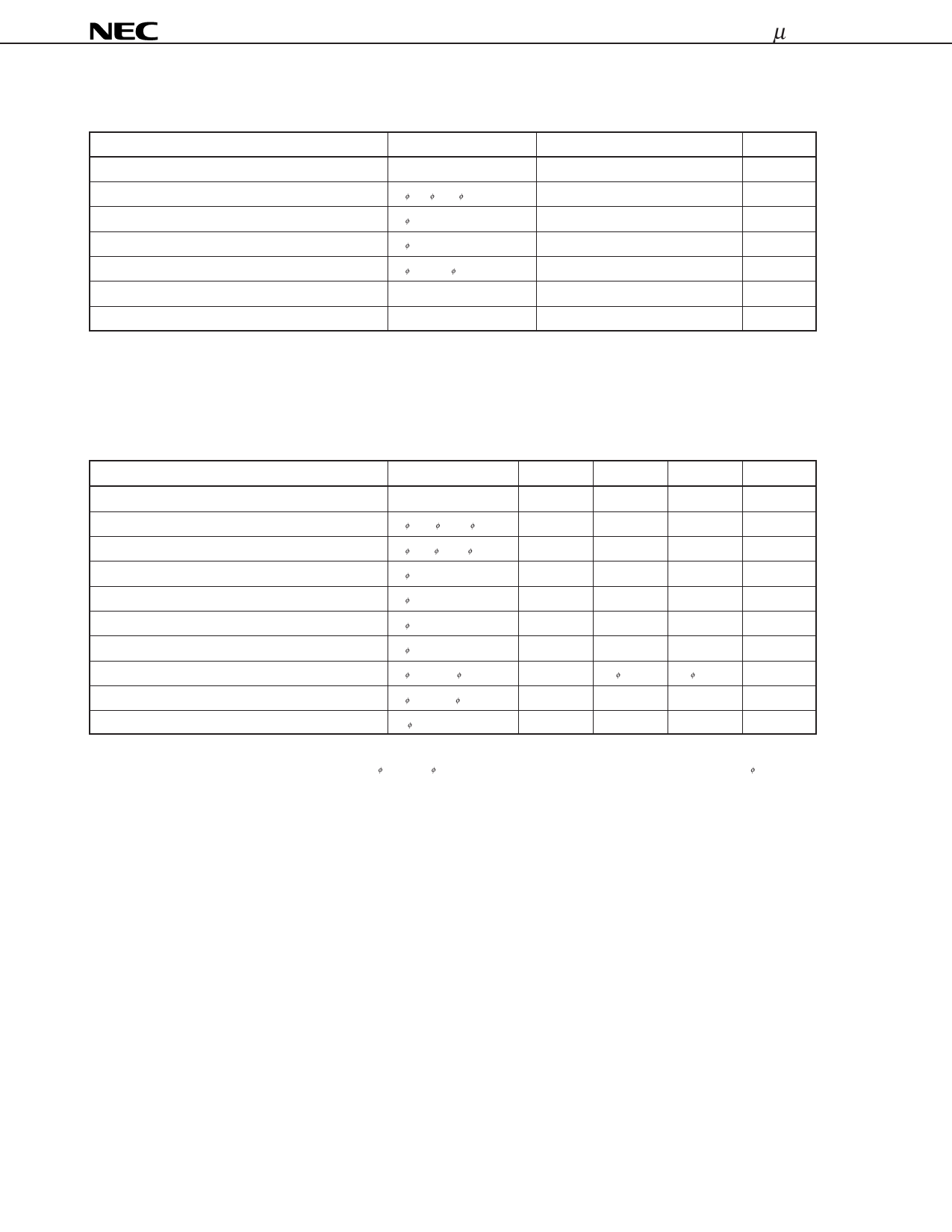

ABSOLUTE MAXIMUM RATINGS (TA = +25 °C)

Parameter

Output drain voltage

Shift register clock voltage

Reset gate clock voltage

Reset feed-through level clamp clock voltage

Transfer gate clock voltage

Operating ambient temperature

Storage temperature

Symbol

VOD

Vφ1, Vφ1L, Vφ2

VφRB

VφCLB

VφTG1 to VφTG3

TA

Tstg

Ratings

Unit

–0.3 to +15

V

–0.3 to +15

V

–0.3 to +15

V

–0.3 to +15

V

–0.3 to +15

V

–25 to +70

°C

–40 to +100

°C

Caution Exposure to ABSOLUTE MAXIMUM RATINGS for extended periods may affect device reliability;

exceeding the ratings could cause permanent damage. The parameters apply independently.

RECOMMENDED OPERATING CONDITIONS (TA = +25 °C)

Parameter

Output drain voltage

Shift register clock high level

Shift register clock low level

Reset gate clock high level

Reset gate clock low level

Reset feed-through level clamp clock high level

Reset feed-through level clamp clock low level

Transfer gate clock high level

Transfer gate clock low level

Data rate

Symbol

VOD

Vφ1H, Vφ1LH, Vφ2H

Vφ1L, Vφ1LL, Vφ2L

VφRBH

VφRBL

VφCLBH

VφCLBL

VφTG1H to VφTG3H

VφTG1L to VφTG3L

2fφRB

MIN.

11.4

4.5

–0.3

4.5

–0.3

4.5

–0.3

4.5

–0.3

–

TYP.

12.0

5.0

0

5.0

0

5.0

0

Vφ1HNote

0

2

MAX.

12.6

5.5

+0.5

5.5

+0.5

5.5

+0.5

Vφ1HNote

+0.5

30

Unit

V

V

V

V

V

V

V

V

V

MHz

Note When Transfer gate clock high level (VφTG1H to VφTG3H) is higher than Shift register clock high level (Vφ1H), Image

lag can increase.

4