K7R161884B-FC20(2004) Просмотр технического описания (PDF) - Samsung

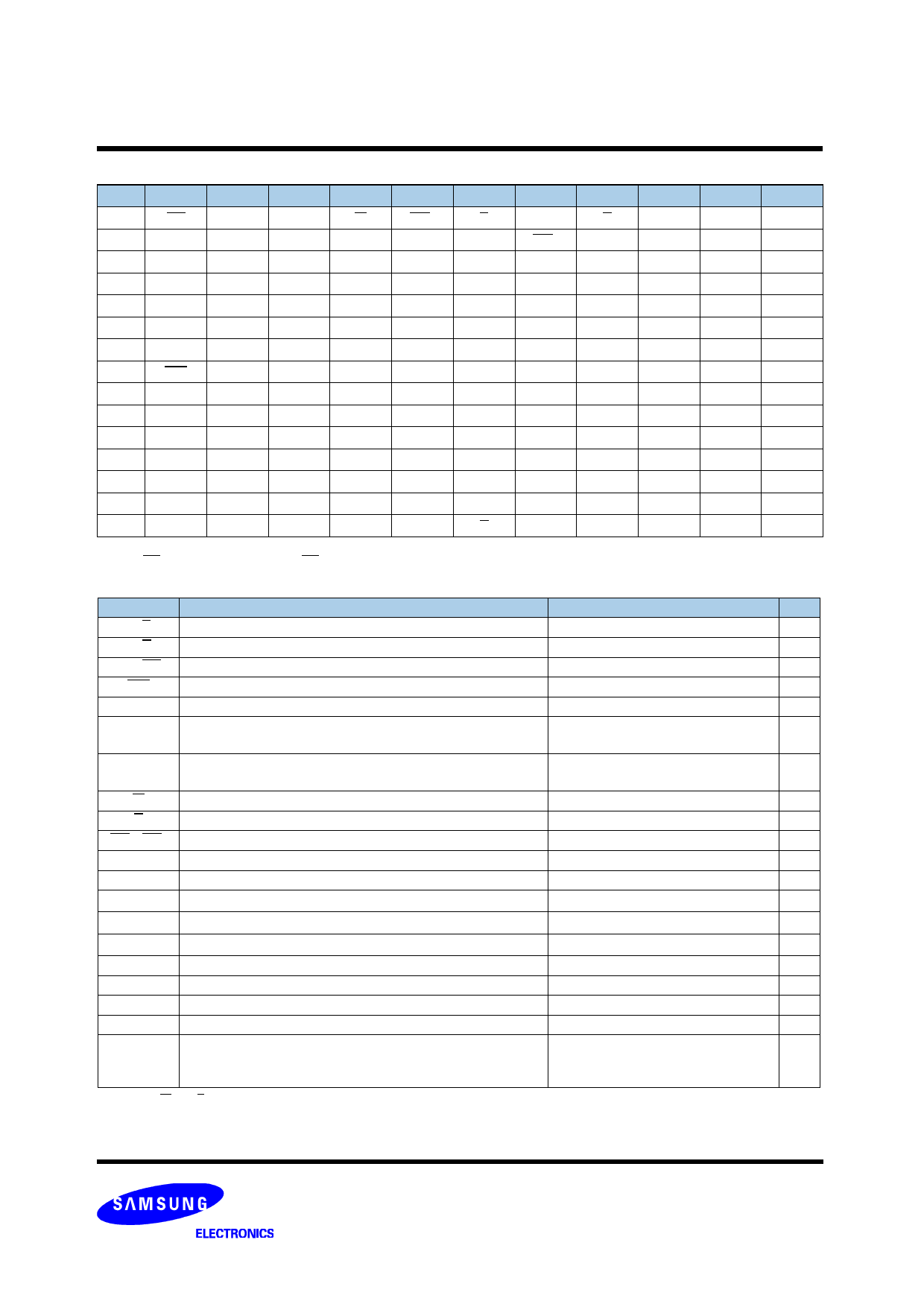

Номер в каталоге

Компоненты Описание

производитель

K7R161884B-FC20 Datasheet PDF : 18 Pages

| |||

K7R163684B

K7R161884B

512Kx36 & 1Mx18 QDRTM II b4 SRAM

GENERAL DESCRIPTION

The K7R163684B and K7R161884B are 18,874,368-bits QDR(Quad Data Rate)

Synchronous Pipelined Burst SRAMs.

They are organized as 524,288 words by 36bits for K7R163684B and 1,048,576 words by 18 bits for K7R161884B.

The QDR operation is possible by supporting DDR read and write operations through separate data output and input ports

with the same cycle. Memory bandwidth is maxmized as data can be transfered into sram

on every rising edge of K and K, and transfered out of sram on every rising edge of C and C.

And totally independent read and write ports eliminate the need for high speed bus turn around.

Address for read and write are latched on alternate rising edges of the input clock K.

Data inputs, and all control signals are synchronized to the input clock ( K or K ).

Normally data outputs are synchronized to output clocks ( C and C ), but when C and C are tied high,

the data outputs are synchronized to the input clocks ( K and K ).

Read data are referenced to echo clock ( CQ or CQ ) outputs.

Common address bus is used to access address both for read and write operations.

The internal burst counter is fiexd to 4-bit sequential for both read and write operations, reguiring tow full clock bus cycles.

Any request that attempts to interrupt a burst operation in progress is ignored.

Synchronous pipeline read and late write enable high speed operations.

Simple depth expansion is accomplished by using R and W for port selection.

Byte write operation is supported with BW0 and BW1 ( BW2 and BW3 ) pins.

IEEE 1149.1 serial boundary scan (JTAG) simplifies monitoring package pads attachment status with system.

The K7R163684B and K7R161884B are implemented with SAMSUNG's high performance 6T CMOS technology

and is available in 165pin FBGA packages. Multiple power and ground pins minimize ground bounce.

Read Operations

Read cycles are initiated by activating R at the rising edge of the positive input clock K.

Address is presented and stored in the read address register synchronized with K clock.

For 4-bit burst DDR operation, it will access four 36-bit or 18-bit data words with each read command.

The first pipelined data is transfered out of the device triggered by C clock following next K clock rising edge.

Next burst data is triggered by the rising edge of following C clock rising edge.

The process continues until all four data are transfered.

Continuous read operations are initated with K clock rising edge.

And pipelined data are transferred out of device on every rising edge of both C and C clocks.

In case C and C tied to high, output data are triggered by K and K insted of C and C.

When the R is disabled after a read operation, the K7R163684B and K7R161884B will first complete

burst read operation

before entering into deselect mode at the next K clock rising edge.

Then output drivers disabled automatically to high impedance state.

Echo clock operation

To assure the output tracibility, the SRAM provides the output Echo clock, pair of compliment clock CQ and CQ,

which are synchronized with internal data output.

Echo clocks run free during normal operation.

The Echo clock is triggered by internal output clock signal, and transfered to external through same structures

as output driver.

-5-

July. 2004

Rev 3.1