INTEL386 Просмотр технического описания (PDF) - Intel

Номер в каталоге

Компоненты Описание

производитель

INTEL386 Datasheet PDF : 102 Pages

| |||

Intel386TM SX MICROPROCESSOR

EFLAGS REGISTER

CONTROL REGISTERS

The flag register is a 32-bit register named EFLAGS

The defined bits and bit fields within EFLAGS

shown in Figure 2 2 control certain operations and

indicate the status of the Intel386 SX Microproces-

sor The lower 16 bits (bits 0–15) of EFLAGS con-

tain the 16-bit flag register named FLAGS This is

the default flag register used when executing 8086

80286 or real mode code The functions of the flag

bits are given in Table 2 1

The Intel386 SX Microprocessor has three control

registers of 32 bits CR0 CR2 and CR3 to hold the

machine state of a global nature These registers

are shown in Figures 2 1 and 2 2 The defined CR0

bits are described in Table 2 2

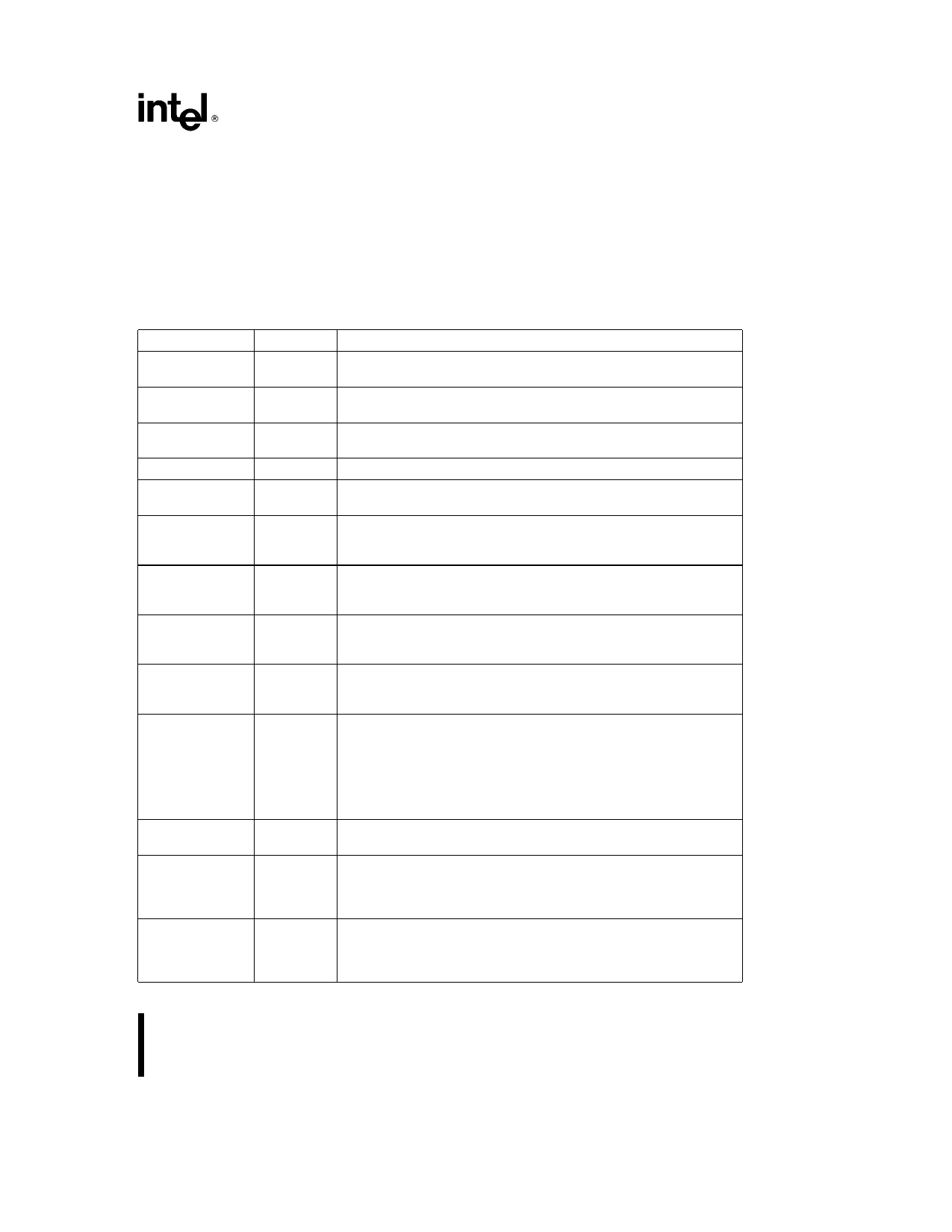

Bit Position

0

2

4

6

7

8

9

10

11

12 13

14

16

17

Name

CF

PF

AF

ZF

SF

TF

IF

DF

OF

IOPL

NT

RF

VM

Table 2 1 Flag Definitions

Function

Carry Flag Set on high-order bit carry or borrow cleared

otherwise

Parity Flag Set if low-order 8 bits of result contain an even

number of 1-bits cleared otherwise

Auxiliary Carry Flag Set on carry from or borrow to the low

order four bits of AL cleared otherwise

Zero Flag Set if result is zero cleared otherwise

Sign Flag Set equal to high-order bit of result (0 if positive 1 if

negative)

Single Step Flag Once set a single step interrupt occurs after

the next instruction executes TF is cleared by the single step

interrupt

Interrupt-Enable Flag When set maskable interrupts will cause

the CPU to transfer control to an interrupt vector specified

location

Direction Flag Causes string instructions to auto-increment

(default) the appropriate index registers when cleared Setting

DF causes auto-decrement

Overflow Flag Set if the operation resulted in a carry borrow

into the sign bit (high-order bit) of the result but did not result in a

carry borrow out of the high-order bit or vice-versa

I O Privilege Level Indicates the maximum Current Privilege

Level (CPL) permitted to execute I O instructions without

generating an exception 13 fault or consulting the I O permission

bit map while executing in protected mode For virtual 86 mode it

indicates the maximum CPL allowing alteration of the IF bit See

Section 4 2 for a further discussion and definitions on various

privilege levels

Nested Task Set if the execution of the current task is nested

within another task Cleared otherwise

Resume Flag Used in conjunction with debug register

breakpoints It is checked at instruction boundaries before

breakpoint processing If set any debug fault is ignored on the

next instruction

Virtual 8086 Mode If set while in protected mode the Intel386

SX Microprocessor will switch to virtual 8086 operation handling

segment loads as the 8086 does but generating exception 13

faults on privileged opcodes

9