IDT72V36102 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

производитель

IDT72V36102 Datasheet PDF : 29 Pages

| |||

IDT72V3682/72V3692/72V36102 3.3V CMOS SyncBiFIFOTM

16,384 x 36 x 2, 32,768 x 36 x 2 and 65,536 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

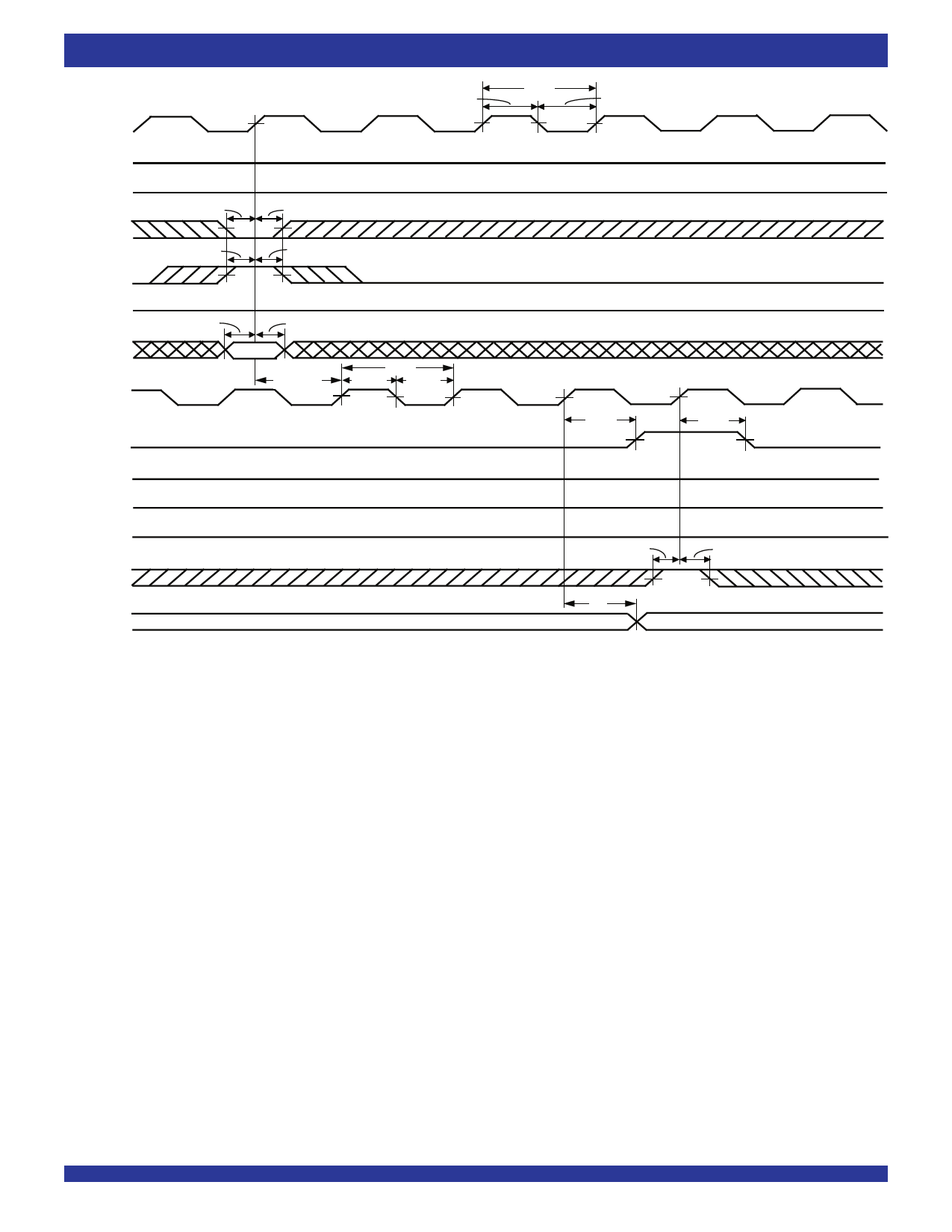

CLKB

tCLKH

tCLK

tCLKL

CSB LOW

W/RB LOW

MBB

tENS2

tENS2

tENH

tENH

ENB

IRB HIGH

tDS

tDH

B0 - B35

CLKA

W1

(1)

tSKEW1

tCLK

tCLKH tCLKL

1

2

ORA FIFO2 Empty

CSA LOW

W/RA LOW

MBA LOW

ENA

A0 -A35

Old Data in FIFO2 Output Register

3

tPOR

tPOR

tENS2

tA

tENH

W1

4679 drw 13

NOTE:

1. tSKEW1 is the minimum time between a rising CLKB edge and a rising CLKA edge for ORA to transition HIGH and to clock the next word to the FIFO2 output register in three CLKA cycles.

If the time between the rising CLKB edge and rising CLKA edge is less than tSKEW1, then the transition of ORA HIGH and load of the first word to the output register may occur one CLKA

cycle later than shown.

Figure 10. ORA Flag Timing and First Data Word Fall Through when FIFO2 is Empty (FWFT Mode)

19