GS9021A Просмотр технического описания (PDF) - Gennum -> Semtech

Номер в каталоге

Компоненты Описание

производитель

GS9021A Datasheet PDF : 26 Pages

| |||

1.3 Parallel Digital Video Data Outputs

PIN

DOUT[9:0]

LSB_TOP

LOGIC OPR

HOST BIT

The output of the device is 10-bit digital video data and is

present on the DOUT[9:0] output pins. The latency through

the device is 8 clock cycles and is illustrated in Figure 3.

The default position of the LSB is DOUT0. Asserting the

LSB_TOP pin HIGH on the GS9021A reverses the order of

the output bits, placing the LSB at DOUT9 and simplifying

board layout in some applications. Figure 11 shows a

simple application circuit illustrating the connections to the

GS9032.

to as much as four frames when switching between PAL

and NTSC standards. If this delay is intolerable, the user

can manually set the standard through the HOSTIF write

table. To set the standard manually, the STD_SEL bit must

be set HIGH and the S bit and STD[3:0] bits set

accordingly. The default standard upon resetting the device

is NTSC 4:2:2 component (13.5MHz Y sampling).

The S bit, used for single link data standards only, is

encoded in the TRSID word and indicates if the data is in

RGB or YCRCB format as per SMPTE RP174. In automatic

standard detection mode, the S bit can be read from the

HOSTIF read table. In manual mode, the S bit must be set

in the HOSTIF write table.

2. FLYWHEEL BLOCK

2.1 FVH Flywheel

1.4 Automatic Standard Detection

PIN

LOGIC OPR

HOST BIT

STD_SEL

STD[3:0]

S

The device automatically detects the incoming video

standard. The detected standard is encoded on the

STD[3:0] bits of the HOSTIF read table as shown in Tables 1

and 4.

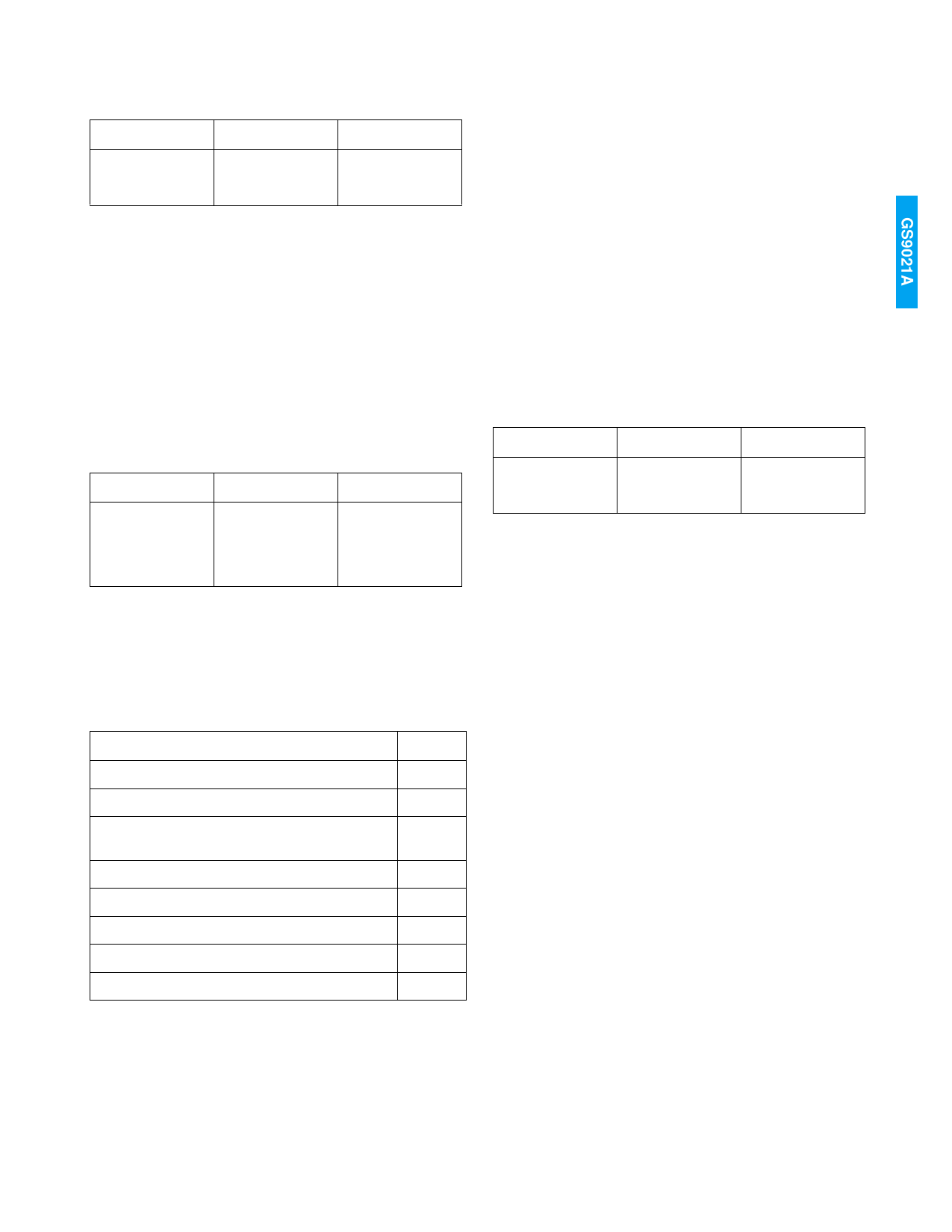

TABLE 1

STANDARD NAME

STD[3:0]

NTSC 4:2:2 Component with 13.5MHz Y sampling

0000

NTSC Composite

0001

NTSC 4:2:2 16x9 Widescreen with 18MHz Y

sampling

0010

NTSC 4:4:4:4 Single Link with 13.5MHz Y sampling

0011

PAL 4:2:2 Component with 13.5MHz Y sampling

0100

PAL Composite

0101

PAL 4:2:2 16x9 Widescreen with 18MHz Y sampling 0110

PAL 4:4:4:4 Single Link with 13.5MHz Y sampling

0111

Noise immunity is included to ensure that momentary signal

corruption does not affect the automatic standards

detection function. This built in noise immunity results in

delayed detection time during power up and when

switching between standards. Delays range from as little as

eight lines when switching between component standards

PIN

FLYWDIS

LOGIC OPR

OR

HOST BIT

FLYWDIS

SWITCHFLYW

The flywheel’s primary function is to provide accurate field,

vertical, and horizontal output signals in the presence of

noisy or error prone input data. Flywheel synchronization is

based on the TRS words in the incoming data stream. The

FVH flywheel synchronizes to the incoming data stream in

less than two fields once the incoming standard has been

detected. Once synchronized, the TRS words in the

incoming data stream and those generated by the flywheel

are constantly compared to ensure that the flywheel

remains synchronized.

Noise insensitivity is accomplished by re-synchronizing the

flywheel to the data stream only if it is not aligned for long

periods of time. For component signals, four mismatches

between the EAV signal in the incoming and flywheel

generated signals over a window of eight lines will trigger

the flywheel to begin re-synchronization.

For composite signals, re-synchronization is triggered by

mismatches in the TRS encoded line numbers or field bits

for seven consecutive lines.

The flywheel can be disabled by asserting the FLYWDIS

control signal HIGH. Disabling the flywheel will remove the

effective noise immunity. In this mode, FVH values will be

decoded directly from the incoming data stream rather than

being decoded from the flywheel. Note that when the

flywheel is disabled, TRS_BLANK and TRS_ INSERT will not

function correctly if enabled. Therefore, if the flywheel is

disabled, then so should TRS_BLANK and TRS_INSERT.

FLYWDIS is available as an input pin and as a bit in the

HOSTIF write table.

7 of 26

19983 - 1