PEEL22LV10AZ Просмотр технического описания (PDF) - International Cmos Technology

Номер в каталоге

Компоненты Описание

производитель

PEEL22LV10AZ Datasheet PDF : 10 Pages

| |||

PEELTM 22LV10AZ

Programmable Clock Options (see Table 1)

A unique feature of the PEEL22LV10AZ is a

programmable clock multiplexer that allows the user to

select true or complement forms of either input pin or

product-term clock sources.

Operates in both 3 Volt and 3.3 Volt Systems

The PEEL22LV10AZ is designed to operate with a VCC

range of 2.7 to 3.6 Volts D.C. This allows operation in

both 3 Volt 10% (battery operated) and 3.3 Volt 10%

(power supply operated) systems. The propagation

delay tPD is 5 ns slower at the lower voltage, but this is

typically not an issue in battery-operated systems (see

Table 6 - A.C. Electrical Characteristics).

Zero Power Feature

The CMOS PEEL22LV10AZ features "Zero-Power"

standby operation for ultra-low power consumption.

With the "Zero-Power" feature, transition-detection

circuitry monitors the inputs, I/Os (including CLK) and

feedbacks. If these signals do not change for a period

of time greater than approximately two tPD's, the outputs

are latched in their current state and the device

automatically powers down. When the next signal

transition is detected, the device will "wake up" for

active operation until the signals stop switching long

enough to trigger the next power-down. (Note that the

tPD is approximately 5 ns. slower on the first transition

from sleep mode.)

100

10

1

0.1

0.01

0.001

0.001

0.01

0.1

1

10

Frequency in MHz

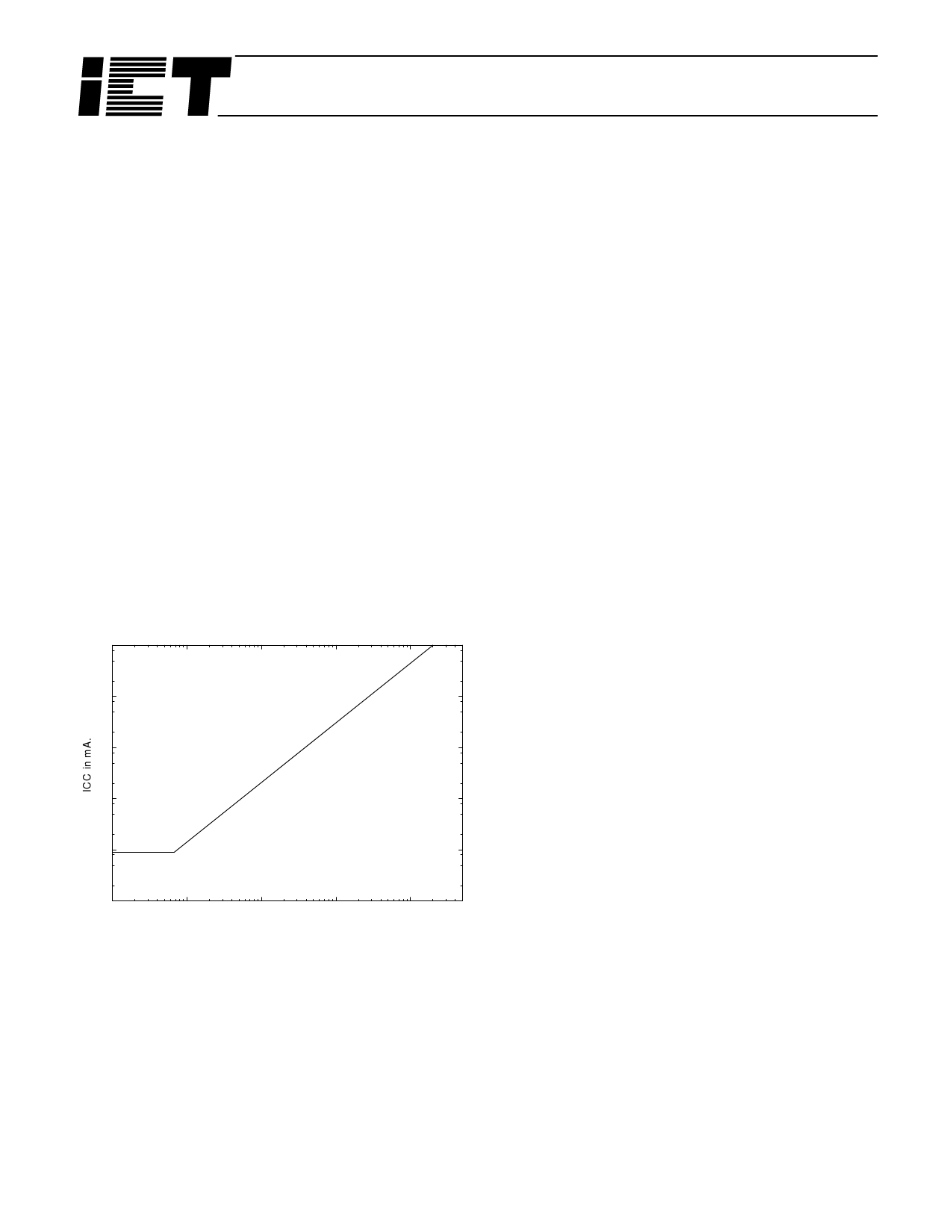

Figure 5 - Typical ICC vs. Input Clock Frequency for

the 22LV10AZ

As a result of the "Zero-Power" feature, significant

power savings can be realized for combinatorial or

sequential operations when the inputs or clock change

at a modest rate. See Figure 5.

When the PEEL22LV10AZ is powered up, a built-in

feature holds the outputs in tri-state until VCC reaches

2.2V. This prevents output transitions during power-up.

Schmitt Trigger Inputs

The PEEL22LV10AZ has Schmitt trigger input buffers

on all inputs, including the clock. Schmitt trigger inputs

allow direct input of slow signals such as biomedical

and sine waves or clocks. They are also useful in

cleaning up noisy signals. This makes the

PEEL22LV10AZ especially desirable in portable

applications where the environment is less predictable.

Design Security

The PEEL22LV10AZ provides a special EEPROM

security bit that prevents unauthorized reading or

copying of designs programmed into the device. The

security bit is set by the PLD programmer, either at the

conclusion of the programming cycle or as a separate

step, after the device has been programmed. Once the

security bit is set it is impossible to verify (read) or

program the PEEL until the entire device has first been

erased with the bulk-erase function.

Signature Word

The signature word feature allows a 64-bit code to be

programmed into the PEEL22LV10AZ if the PEEL

V10A+ software option (see Table 1) is used. The code

can be read back even after the security bit has been

set. The signature word can be used to identify the

pattern programmed into the device or to record the

design revision, etc.

Programming Support

ICT's JEDEC file translator allows easy conversion of

existing 24 pin PLD designs to the PEEL22LV10AZ,

without the need for redesign. ICT supports a broad

range of popular third party design entry systems,

including Data I/O Synario and Abel, Logical Devices

CUPL and others. ICT also offers its proprietary

WinPLACE software, an easy-to-use entry level PC-

based software development system.

Programming support includes all the popular third

party programmers; Data I/O, Logical Devices, and

numerous others.

5

04-02-037D