CY8C5246AXI-038 –ü—Ä–ĺ—Ā–ľ–ĺ—ā—Ä —ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ–ĺ–≥–ĺ –ĺ–Ņ–ł—Ā–į–Ĺ–ł—Ź (PDF) - Cypress Semiconductor

–Ě–ĺ–ľ–Ķ—Ä –≤ –ļ–į—ā–į–Ľ–ĺ–≥–Ķ

–ö–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā—č –ě–Ņ–ł—Ā–į–Ĺ–ł–Ķ

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć

CY8C5246AXI-038 Datasheet PDF : 85 Pages

| |||

PRELIMINARY

PSoC¬ģ5: CY8C52 Family Data Sheet

Vddd. Supply for all digital peripherals and digital core regulator.

Vddd must be less than or equal to Vdda.

Vssa. Ground for all analog peripherals.

XRES (and configurable XRES). External reset pin. Active low

with internal pullup. In 48-pin SSOP parts, P1[2] is configured as

XRES. In all other parts the pin is configured as a GPIO.

Vssb. Ground connection for boost pump.

Vssd. Ground for all digital logic and I/O pins.

Vddio0, Vddio1, Vddio2, Vddio3. Supply for I/O pins. See

pinouts for specific I/O pin to Vddio mapping. Vddio must be less

than or equal to Vdda.

4. CPU

4.1 ARM Cortex-M3 CPU

The CY8C52 family of devices has an ARM Cortex-M3 CPU

core. The Cortex-M3 is a low power 32-bit three-stage pipelined

Harvard architecture CPU that delivers 1.25 DMIPS/MHz. It is

intended for deeply embedded applications that require fast

interrupt handling features.

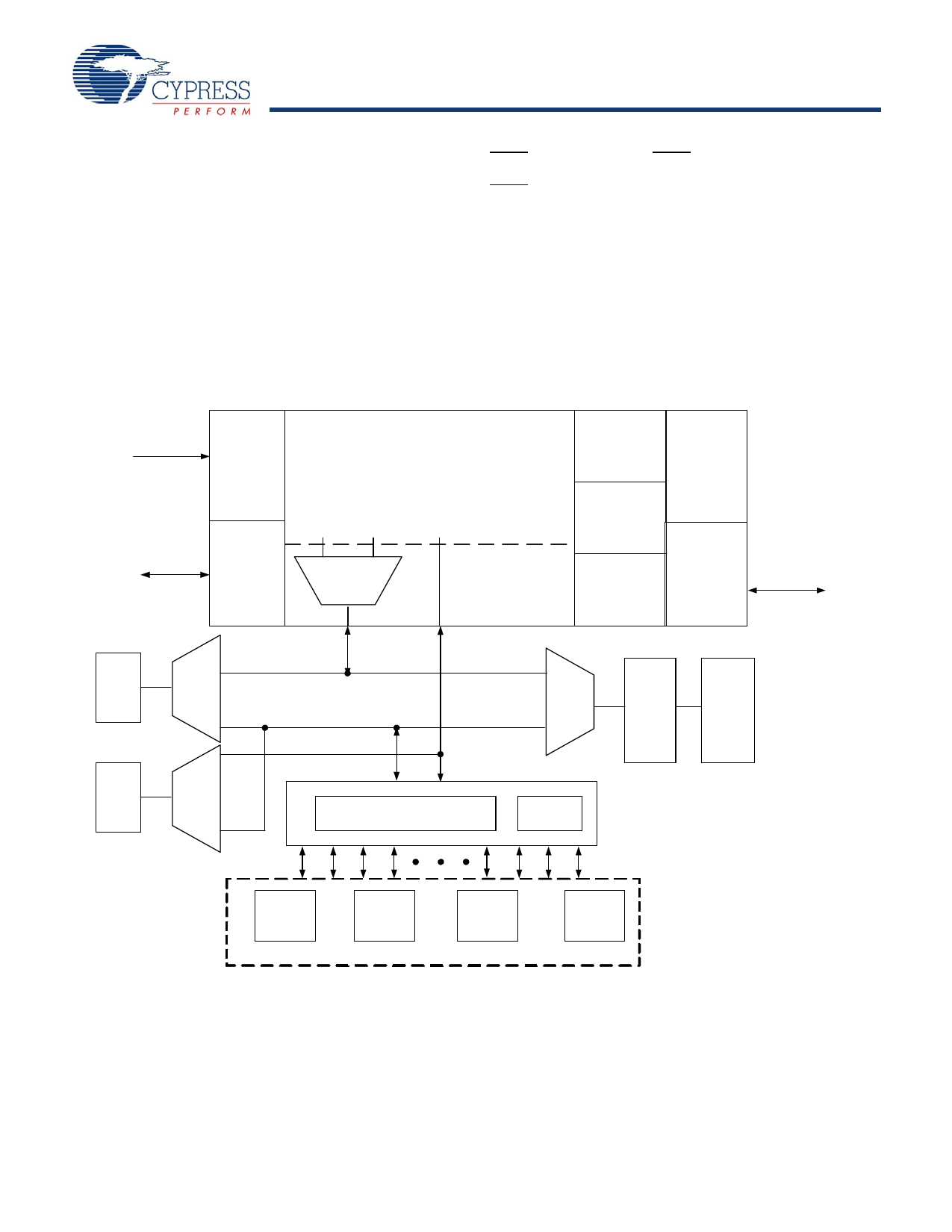

Figure 4-1. ARM Cortex-M3 Block Diagram

Interrupt Inputs

Nested

Vectored

Interrupt

Controller

(NVIC)

JTAG/SWD Debug Block

(Serial and

JTAG)

32 KB

SRAM

Bus

Matrix

Cortex M3 CPU Core

Data

Watchpoint and

Trace (DWT)

Embedded

Trace Module

(ETM)

I- Bus D-Bus

C- Bus

S- Bus

Instrumentation

Trace Module

(ITM)

Cortex M3 Wrapper

Flash Patch

and Breakpoint

(FPB)

Trace Port

Interface Unit

(TPIU)

Trace Pins:

5 for TRACEPORT or

1 for SWV mode

AHB

AHB

Bus

Matrix

Cache

256 KB

ECC

Flash

32 KB

SRAM

Bus

Matrix

AHB Spokes

AHB

AHB Bridge & Bus Matrix

PHUB

DMA

GPIO &

EMIF

Prog.

Digital

Prog.

Analog

Peripherals

Special

Functions

The Cortex-M3 CPU subsystem includes these features:

¬Ą ARM Cortex-M3 CPU

¬Ą Programmable Nested Vectored Interrupt Controller (NVIC),

tightly integrated with the CPU core

¬Ą Full featured debug and trace modules, tightly integrated with

the CPU core

¬Ą Up to 256 KB of Flash memory, 2 KB of EEPROM, and 64 KB

of SRAM

¬Ą Cache controller

¬Ą Peripheral HUB (PHUB)

¬Ą DMA controller

¬Ą External Memory Interface (EMIF)

Document Number: 001-55034 Rev. *A

Page 10 of 85

[+] Feedback