CY8C3246LTI-156 –Я—А–Њ—Б–Љ–Њ—В—А —В–µ—Е–љ–Є—З–µ—Б–Ї–Њ–≥–Њ –Њ–њ–Є—Б–∞–љ–Є—П (PDF) - Cypress Semiconductor

–Э–Њ–Љ–µ—А –≤ –Ї–∞—В–∞–ї–Њ–≥–µ

–Ъ–Њ–Љ–њ–Њ–љ–µ–љ—В—Л –Ю–њ–Є—Б–∞–љ–Є–µ

–њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М

CY8C3246LTI-156 Datasheet PDF : 119 Pages

| |||

PSoC¬Ѓ 3: CY8C32 Family

Data Sheet

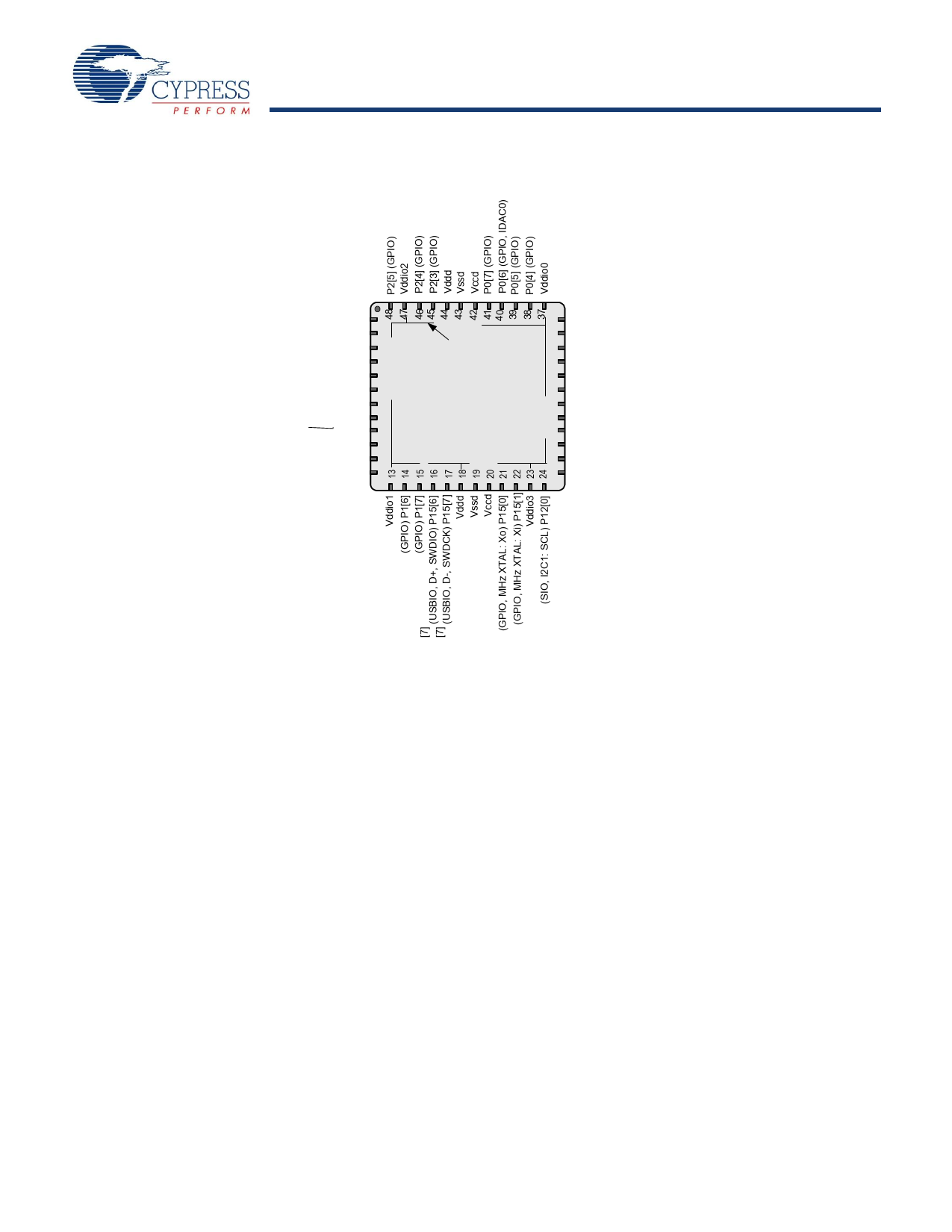

Figure 2-2. 48-pin QFN Part Pinout[8]

(GPIO) P2[6] 1

(GPIO) P2[7] 2

Vssb 3

Ind 4

Vboost 5

Vbat 6

(GPIO, TMS, SWDIO) P1[0] 7

(GPIO, TCK, SWDCK) P1[1] 8

(GPIO, Configurable XRES) P1[2] 9

(GPIO, TDO, SWV) P1[3] 10

(GPIO, TDI) P1[4] 11

(GPIO, nTRST) P1[5] 12

Lines show

Vddio to I/O

supply

association

QFN

( Top View)

36 P0[3] (Extref0, GPIO)

35 P0[2] (GPIO)

34 P0[1] (GPIO)

33 P0[0] (GPIO)

32 P12[3] (SIO)

31 P12[2] (SIO)

30 Vdda

29 Vssa

28 Vcca

27 P15[3] (GPIO, kHz XTAL: Xi)

26 P15[2] (GPIO, kHz XTAL: Xo)

25 P12[1] (SIO, I2C1: SDA)

Notes

7. The center pad on the QFN package should be connected to digital ground (Vssd) for best mechanical, thermal, and electrical performance. If not connected to

ground, it should be electrically floated and not connected to any other signal.

8. PPins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

Document Number: 001-56955 Rev. *J

Page 6 of 119

[+] Feedback