CY7C9235-270JC Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CY7C9235-270JC Datasheet PDF : 8 Pages

| |||

PRELIMINARY

CY7C9235

Pin Descriptions (continued)

CY7C9235 SMPTE-259M Encoder

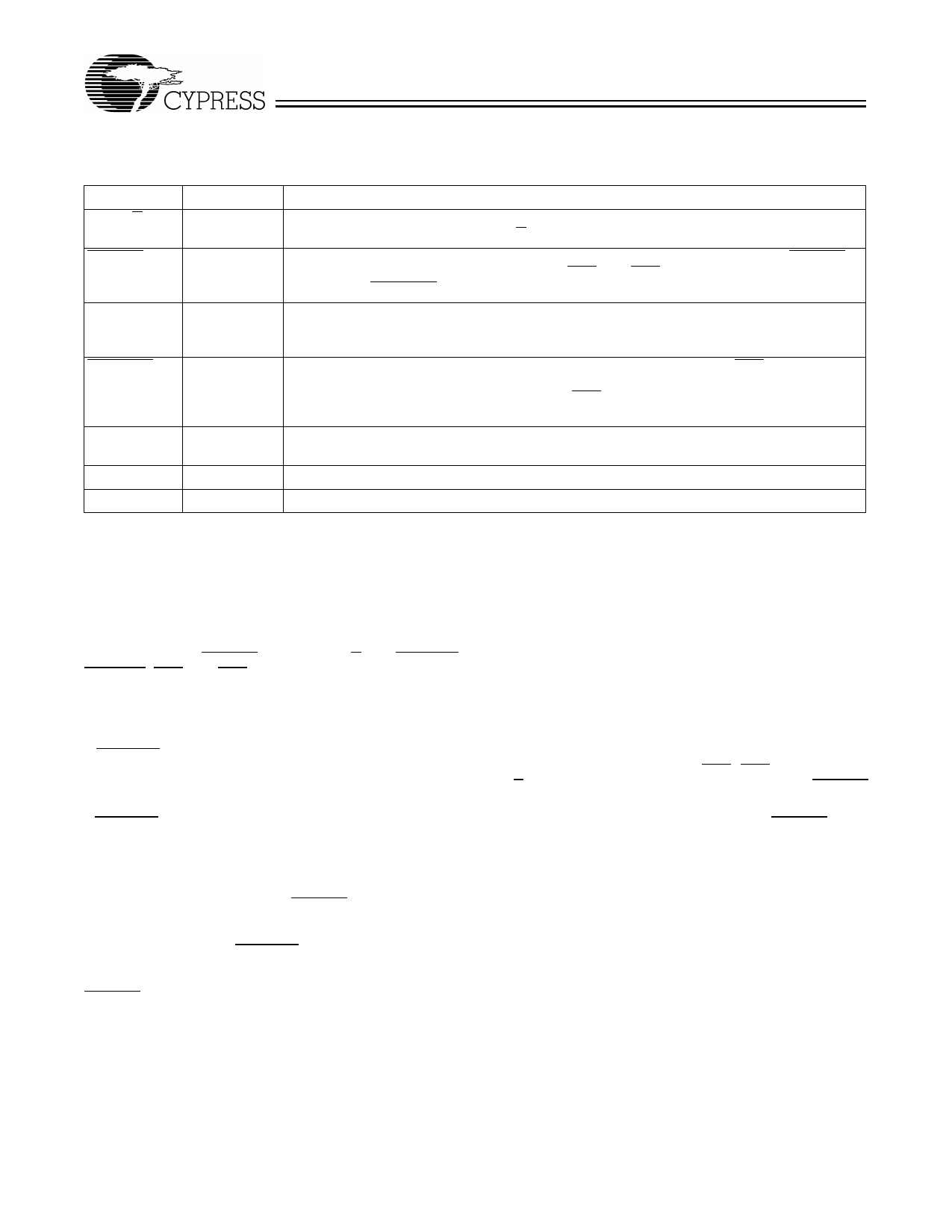

Name

Q0(SC/D)

DVB_EN

I/O

Output

Input

CKW

Input

ENA_OUT Output

OE

Input

VCC

VSS

Description

Output Bit 0. This is the LSB of the output register. It should be connected directly to the

CY7B9234 serializer input signal SC/D(Da).

DVB Mode Enable. This signal is sampled by the rising edge of the CKW clock. If DVB_EN is

active (LOW), the data present on the PD0−9, ENA, and ENN inputs are latched and routed to

the Q0−9 and ENA_OUT outputs.

Clock Write. This clock controls all synchronous operations of the CY7C9235. It operates at the

character rate which is equivalent to one tenth the serialized bit-rate. This clock also connects

directly to the CKW input of the CY7B9234 serializer.

Enable Parallel Data Out. This output attached directly to the CY7B9234 ENA input, and iden-

tifies when valid data is available at the CY7C9235 outputs. If used only for SMPTE-259M data

streams, this output may be left open, with the ENA input to the CY7B9234 directly connected

to VSS.

Output Enable. When this signal is HIGH all outputs are driven to their normal logic levels. When

LOW, all outputs are placed in a High-Z state.

Power.

Ground.

CY7C9235 Description

Input Register

The input register is clocked by the rising edge of CKW. This

register captures the data present at the PD0−9 inputs on every

clock cycle. In addition to the data inputs, all control inputs

except OE are also captured at each rising edge of CKW. This

includes BYPASS, DVB_EN, SVS_EN, SC/D_EN, TRS_DET,

TRS_FILT, ENN, and ENA.

TRS Filter

The TRS Filter is used to convert all 8-bit TRS characters

(000–003 and 3FC–3FF in 10-bit hex) to their full 10-bit value.

If TRS_FILT is active (LOW) and any of these values are de-

tected in the input register, the lower two bits are forced to

either zeros or ones respectively. This allows the encoder to

be used with both 8- and 10-bit SMPTE character streams.

If TRS_FILT is HIGH, the filter function is disabled and all char-

acters are passed from the input register to the SMPTE scram-

bler unmodified.

TRS Detector

When operated in SMPTE mode (DVB_EN is HIGH), the TRS

detector looks for the most significant eight bits of the input

register to be either all ones or all zeros. If either of these

values are detected, the TRS_DET output will go LOW follow-

ing the rising edge of CKW, and remain LOW until a character

is detected in the input register that is not all zeros or ones, or

DVB_EN is latched LOW.

SMPTE Scrambler

The SMPTE scrambler implements a parallel encoded version

of a linear-feedback shift register. It encodes the data present

in the input register using the X9 + X4 + 1 polynomial to in-

crease the transition density of the serial data stream and to

decrease the DC-content of the transmitted serial bit stream.

NRZI Encoder

The scrambled data is also fed through an NRZ-to-NRZI en-

coder. This also increases the transition density of the serial

data stream, decreases the DC-content of the transmitted se-

rial bit stream, and makes the serial stream insensitive to po-

larity inversions.

DVB-ASI Operation

The CY7C9235 is designed to operate in both SMPTE-259M

and DVB-ASI environments. When operated in SMPTE-only

environments, the DVB control inputs may be tied to either

VCC or VSS as needed to place them in a known state. When

not used for DVB operation, the ENA, ENN, SVS_EN, and

SC/D_EN inputs many be tied to either VCC or VSS. DVB_EN

must be tied or driven HIGH.

DVB-ASI operation is enabled by asserting DVB_EN LOW.

This signal is latched by the rising edge of the CKW clock.

When the CY7C9235 is placed in DVB mode, the SMPTE and

NRZI encoders are bypassed, and the data latched into the

input register is routed directly to the output register.

Error Propagation

For those DVB-ASI implementations that do not require prop-

agation of detected errors, the Q9 output may be forced to a

zero by setting SVS_EN LOW. When SVS_EN is HIGH (and

the encoder is in DVB mode) the PD9 data latched into the

input register is routed to the output register and to the

CY7B9234 SVS input.

Command Code Generation

The DVB-ASI interface does not normally transmit any com-

mand characters other than the K28.5 code that is used both

for synchronization and as a fill character when data is not

being transmitted. These K28.5 characters may be generated

by two methods; by controlling when the CY7C9235 is enabled

Document #: 38-02012 Rev. *A

Page 4 of 8