CY3685 Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CY3685 Datasheet PDF : 9 Pages

| |||

CY7C68023/CY7C68024

EZ-USB NX2LP™ USB 2.0 NAND Flash Controller

1.0 Features

• High (480-Mbps) or full (12-Mbps) speed USB support

• Both common NAND page sizes supported

— 512bytes –Up to 1Gbit Capacity

— 2K bytes –Up to 8Gbit Capacity

• 8 chip enable pins

— Up to 8 NAND Flash single-device chips

— Up to 4 NAND Flash dual-device chips

• Industry standard ECC NAND Flash correction

— 1-bit per 256 correction

— 2-bit error detection

• Industry standard (SmartMedia) page management for

wear leveling algorithm, bad block handling, and Physical

to Logical management.

• Supports 8-bit NAND Flash interfaces

• Supports 30ns, 50ns, 100ns NAND Flash timing

• Complies with USB Mass Storage Class Specification rev

1.0

• CY7C68024 complies with USB 2.0 Specification for Bus-

Powered Devices (TID# 40460274)

• 43-mA Typical Active Current

• Space-saving and lead-free 56-QFN package (8mm ×

8mm)

• Support for board-level manufacturing test via USB

interface

• 3.3V NAND Flash operation

• NAND Flash power management support

2.0 Introduction

™ The EZ-USB NX2LP (NX2LP) implements a USB 2.0 NAND

Flash controller. This controller adheres to the Mass Storage

Class Bulk-Only Transport Specification. The USB port of the

NX2LP is connected to a host computer directly or via the

downstream port of a USB hub. Host software issues

commands and data to the NX2LP and receives status and

data from the NX2LP using standard USB protocol.

The NX2LP supports industry leading 8-bit NAND Flash inter-

faces and both common NAND page sizes of 512 and 2k

bytes. Eight chip enable pins allow the NX2LP to be connected

to up to eight single- or four dual-device NAND Flash chips.

Certain NX2LP features are configurable, enabling the NX2LP

to meet the needs of different designs’ requirements.

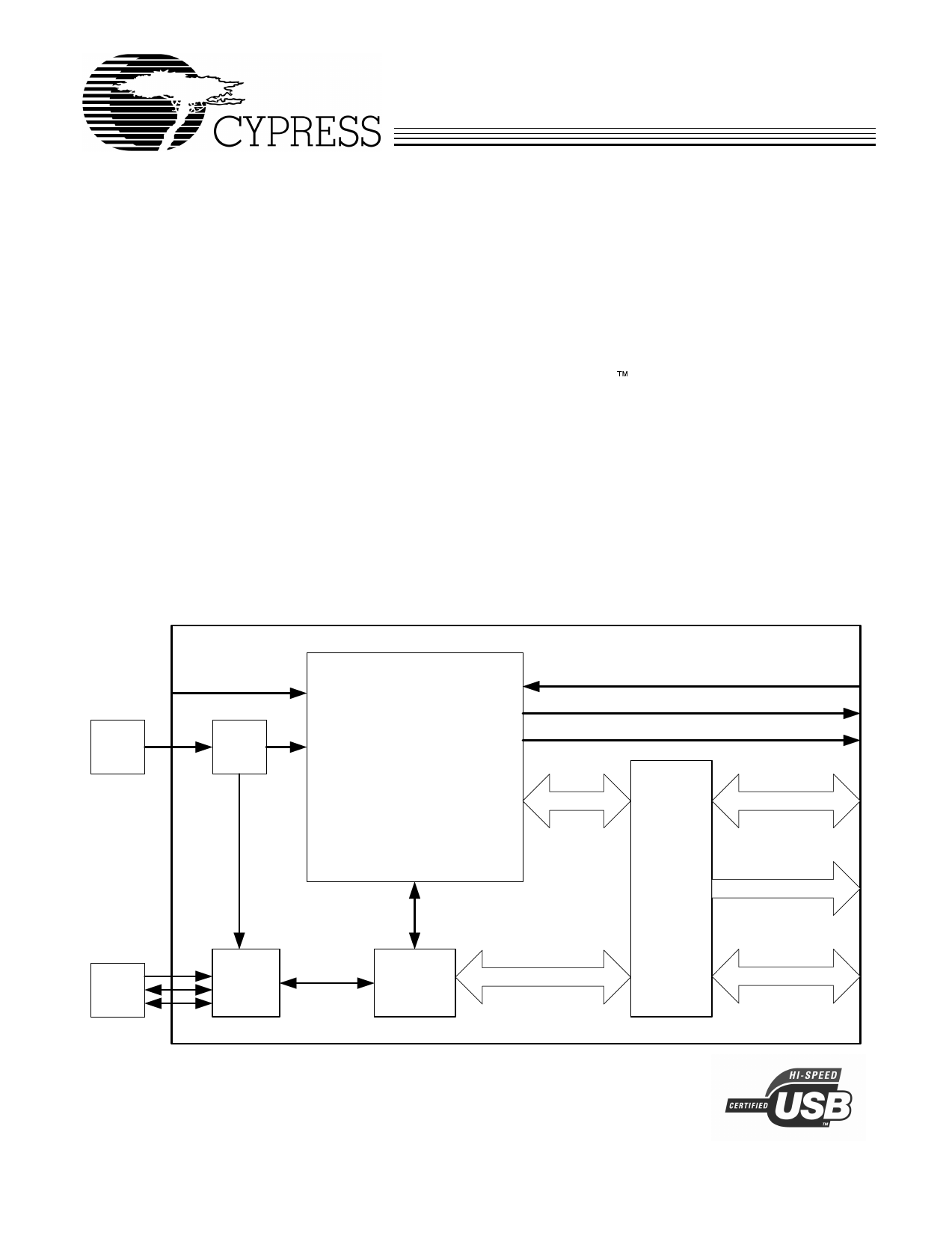

24 MHz

Xtal

Chip Reset

PLL

VBUS

D+

D-

USB 2.0

Xceiver

EZ-USB NX2LP

Internal Control Logic

Control

Write Protect

LED2#

LED1#

NAND Control Signals

NAND Flash

Interface

Logic

Chip Enable Signals

Smart HS/

FS USB

Engine

Data

Figure 1-1. NX2LP Block Diagram

8-bit Data Bus

Cypress Semiconductor Corporation

Document #: 38-08055 Rev. *A

• 3901 North First Street

• San Jose, CA 95134 • 408-943-2600

Revised March 16, 2005