CXD1196 Просмотр технического описания (PDF) - Sony Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CXD1196 Datasheet PDF : 28 Pages

| |||

CXD1196AR

2. Register Functions

2.1 Write register

2.1.1 Register address (REGADR) register

This register is used for selection of the internal registers.

(1) When A0 = XCS = ‘L’, the REGADR register is selected. When A0 = ‘H’ and XCS = ‘L’, the register

specified by the REGADR is selected.

(2) When the low order 4 bits of REGADR are not 0 (hex), and a register write or read is made by setting

A0 = ‘H’ and XCS = ‘L’, the low order 4 bits of REGADR are incremented.

(3) REGADR is cleared by rising edge of DMAEN bit (bit3) of the DMACTL register. (Cleared to 00 (hex).)

2.1.2 DRIVE Interface (DRVIF) register

Bit7 XSLOW (/SLOW SPEED)

‘H’ : A DMA cycle is performed in 4 clocks.

In this case, a standard SRAM with an access time of less than 120 nsec can be connected

to the CXD1196AR.

‘L’ : A DMA cycle is performed in 12 clocks. When the CXD1196R is connected to an SRAM

with a slower access time, set this bit at ‘L’. In this case, a standard SRAM with an access

time of less than 320 ns can be connected to the CXD1196AR. For operation at VDD = 3.5

V, set this bit to L.

Bit6 C2PL1ST (C2PO Ler-byte 1st)

‘H’ : To input two bytes of DATA input, each with a C2PO identifying the lower or upper byte, in

the order of the lower and upper bytes

‘L’ : To input two bytes of DATA input, each with a C2PO identifying the upper or lower byte, in

the order of the upper and lower bytes.

Here, the upper byte means the 8 (eight) upper bits including the MSB from the DSP for CD. And the lower

byte means the 8 (eight) lower bits including the LSB from the DSP for CD. For example, the minute byte

of the Header is a lower byte and the sec byte is a upper byte.

Bit5 LCHLOW (LCH LOW)

‘H’ : To determine that the data is Lch data when LRCK = ‘L’

‘L’ : To determine that the data is Lch data when LRCK = ‘H’

Bit4 BCKRED (BCLK Rising Edge)

‘H’ : To strobe DATA by the rising edge of BCLK

‘L’ : To strobe DATA by the falling edge of BCLK

Bit3, 2 BCKMD1, 0 (BCLK Mode 1, 0)

Set these bits, depending on the number of BCLK clocks output by the DSP for CD during a cycle of

WCLK.

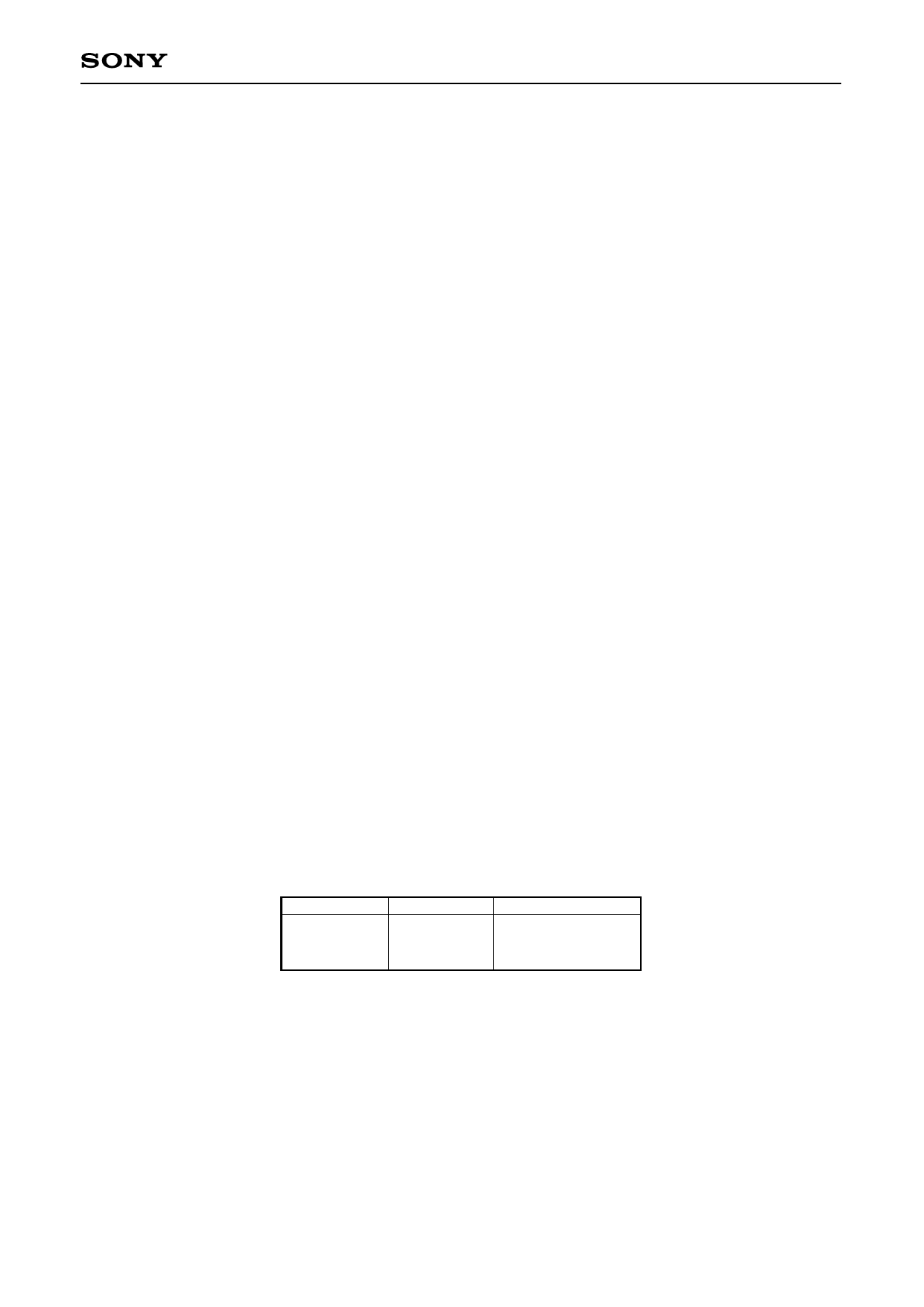

BCKMD1

‘L’

‘L’

‘H’

BCKMD0

‘L’

‘H’

‘X’

16BCLKs/WCLK

24BCLKs/WCLK

32BCLKs/WCLK

Bit1 LSB 1ST (LSB First)

‘H’ : To connect to a DSP for CD which outputs DATA on an LSB first basis

‘L’ : To connect to a DSP for CD which outputs DATA on an MSB first basis

Bit0 CLKLOW (CLK LOW)

‘H’ : To fix CLK pin output at ‘L’

‘L’ : To output 8.4672 MHz clock from CLK pin output

The values of the individual bits of this register must be changed with the decoder in the disabled state.

Table 2.1.1 shows the values of bits of bit 6 through 1 to be set when the CXD1196AR is connected to

Sony DSPs for CD. Fig. 2.2.1 (1) through (3) show input timing charts.

—17—