AT49BV8192A-10CI Просмотр технического описания (PDF) - Atmel Corporation

Номер в каталоге

Компоненты Описание

производитель

AT49BV8192A-10CI Datasheet PDF : 16 Pages

| |||

AT49BV008A(T)/8192A(T)

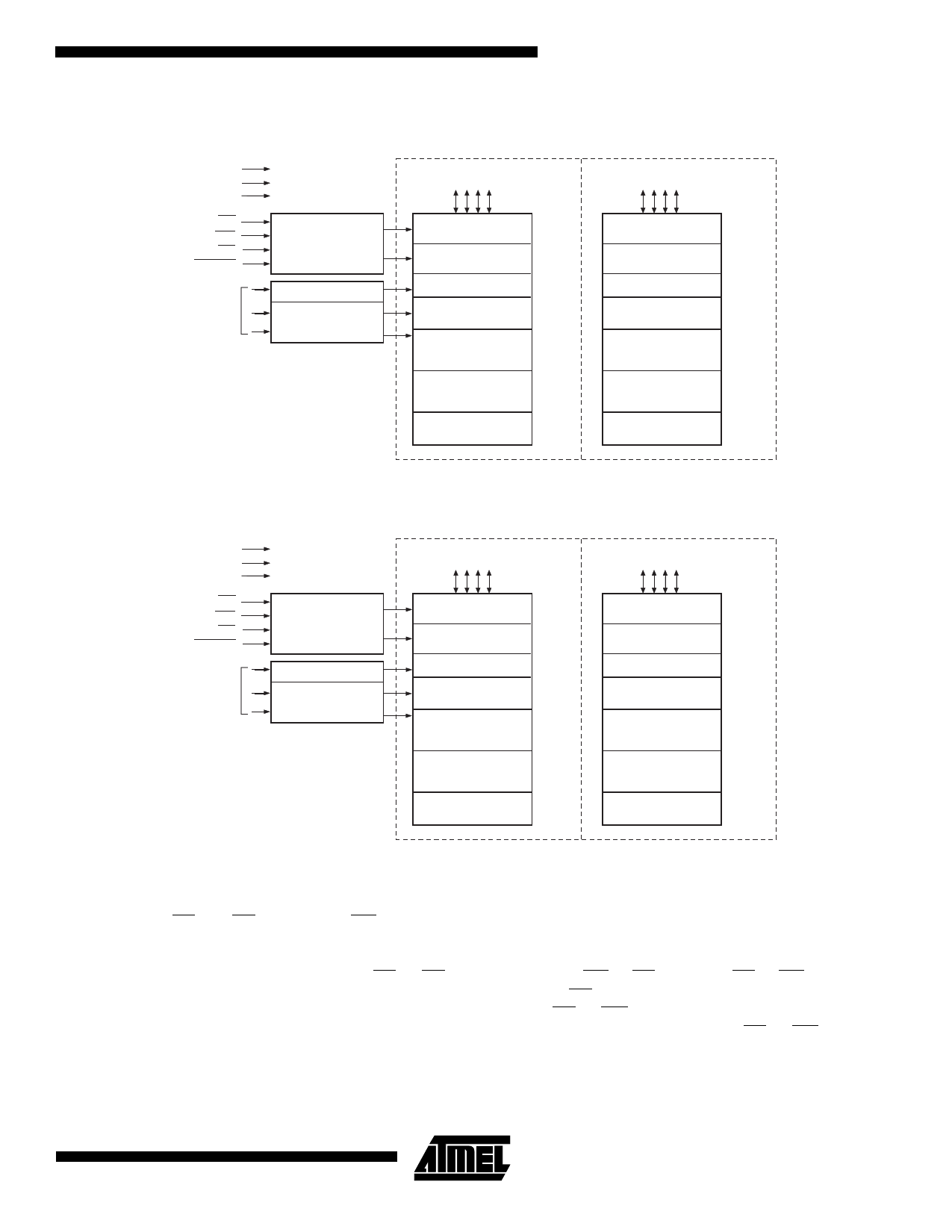

AT49BV008A(T) Block Diagram

VCC

VPP

GND

OE

WE

CE

RESET

ADDRESS

INPUTS

CONTROL

LOGIC

Y DECODER

X DECODER

AT49BV008A

DATA INPUTS/OUTPUTS

I/O0 - I/O7

AT49BV008AT

DATA INPUTS/OUTPUTS

I/O0 - I/O7

INPUT/OUTPUT

BUFFERS

PROGRAM DATA

LATCHES

Y-GATING

MAIN MEMORY

(992K BYTES)

PARAMETER

BLOCK 2

8K BYTES

PARAMETER

BLOCK 1

8K BYTES

BOOT BLOCK

16K BYTES

FFFFF

08000

07FFF

06000

05FFF

04000

03FFF

00000

INPUT/OUTPUT

BUFFERS

PROGRAM DATA

LATCHES

Y-GATING

BOOT BLOCK

16K BYTES

PARAMETER

BLOCK 1

8K BYTES

PARAMETER

BLOCK 2

8K BYTES

MAIN MEMORY

(992K BYTES)

FFFFF

FC000

FBFFF

FA000

F9FFF

F8000

F7FFF

00000

AT49BV8192A(T) Block Diagram

VCC

VPP

GND

OE

WE

CE

RESET

ADDRESS

INPUTS

CONTROL

LOGIC

Y DECODER

X DECODER

AT49BV8192A

DATA INPUTS/OUTPUTS

I/O0 - I/O15

AT49BV8192AT

DATA INPUTS/OUTPUTS

I/O0 - I/O15

INPUT/OUTPUT

BUFFERS

PROGRAM DATA

LATCHES

Y-GATING

MAIN MEMORY

(496K WORDS)

PARAMETER

BLOCK 2

4K WORDS

PARAMETER

BLOCK 1

4K WORDS

BOOT BLOCK

8K WORDS

7FFFF

04000

03FFF

03000

02FFF

02000

01FFF

00000

INPUT/OUTPUT

BUFFERS

PROGRAM DATA

LATCHES

Y-GATING

BOOT BLOCK

8K WORDS

PARAMETER

BLOCK 1

4K WORDS

PARAMETER

BLOCK 2

4K WORDS

MAIN MEMORY

(496K WORDS)

7FFFF

7E000

7DFFF

7D000

7CFFF

7C000

7BFFF

00000

Device Operation

READ: The AT49BV008A(T)/8192A(T) is accessed like an

EPROM. When CE and OE are low and WE is high, the

data stored at the memory location determined by the

address pins is asserted on the outputs. The outputs are

put in the high-impedance state whenever CE or OE is

high. This dual-line control gives designers flexibility in pre-

venting bus contention.

COMMAND SEQUENCES: When the device is first pow-

ered on it will be reset to the read or standby mode

depending upon the state of the control line inputs. In order

to perform other device functions, a series of command

sequences are entered into the device. The command

sequences are shown in the Command Definitions table

(I/O8 - I/O15 are don’t care inputs for the command codes).

The command sequences are written by applying a low

pulse on the WE or CE input with CE or WE low (respec-

tively) and OE high. The address is latched on the falling

edge of CE or WE, whichever occurs last. The data is

latched by the first rising edge of CE or WE. Standard

microprocessor write timings are used. The address loca-

tions used in the command sequences are not affected by

entering the command sequences.

3