AT25DF081A-SSH-B Просмотр технического описания (PDF) - Atmel Corporation

Номер в каталоге

Компоненты Описание

производитель

AT25DF081A-SSH-B

AT25DF081A-SSH-B Datasheet PDF : 53 Pages

| |||

5. Device Operation

The Atmel® AT25DF081A is controlled by a set of instructions that are sent from a host controller, commonly

referred to as the SPI Master. The SPI Master communicates with the AT25DF081A via the SPI bus which is com-

prised of four signal lines: Chip Select (CS), Serial Clock (SCK), Serial Input (SI), and Serial Output (SO).

The AT25DF081A features a dual-input program mode in which the SO pin becomes an input. Similarly, the device

also features a dual-output read mode in which the SI pin becomes an output. In the Dual-Input Byte/Page Pro-

gram command description, the SO pin will be referred to as the SOI (Serial Output/Input) pin, and in the Dual-

Output Read Array command, the SI pin will be referenced as the SIO (Serial Input/Output) pin.

The SPI protocol defines a total of four modes of operation (mode 0, 1, 2, or 3) with each mode differing in respect

to the SCK polarity and phase and how the polarity and phase control the flow of data on the SPI bus. The

AT25DF081A supports the two most common modes, SPI Modes 0 and 3. The only difference between SPI Modes

0 and 3 is the polarity of the SCK signal when in the inactive state (when the SPI Master is in standby mode and

not transferring any data). With SPI Modes 0 and 3, data is always latched in on the rising edge of SCK and

always output on the falling edge of SCK.

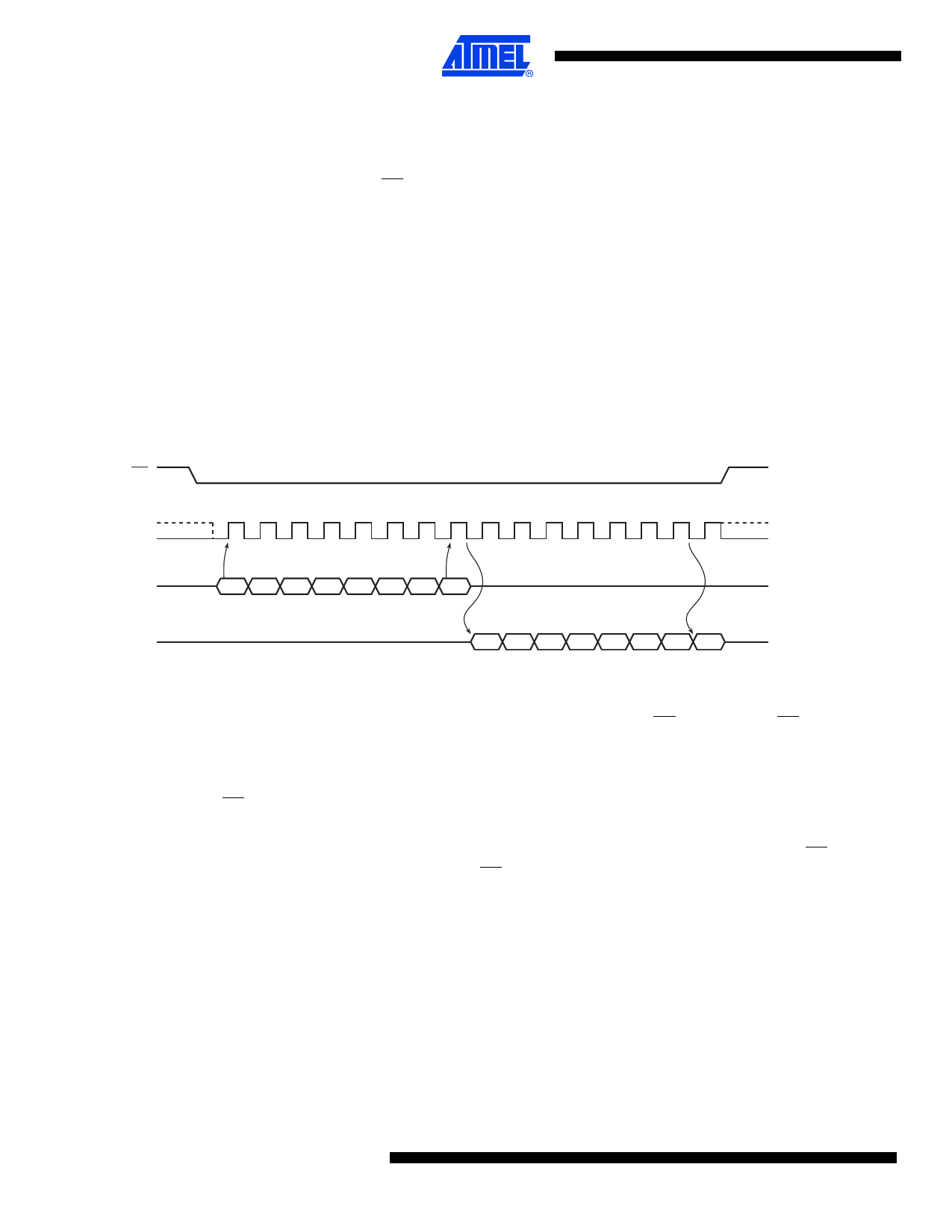

Figure 5-1. SPI Mode 0 and 3

CS

SCK

SI

MSB

LSB

SO

MSB

LSB

6. Commands and Addressing

A valid instruction or operation must always be started by first asserting the CS pin. After the CS pin has been

asserted, the host controller must then clock out a valid 8-bit opcode on the SPI bus. Following the opcode, instruc-

tion dependent information such as address and data bytes would then be clocked out by the host controller. All

opcode, address, and data bytes are transferred with the most-significant bit (MSB) first. An operation is ended by

deasserting the CS pin.

Opcodes not supported by the AT25DF081A will be ignored by the device and no operation will be started. The

device will continue to ignore any data presented on the SI pin until the start of the next operation (CS pin being

deasserted and then reasserted). In addition, if the CS pin is deasserted before complete opcode and address

information is sent to the device, then no operation will be performed and the device will simply return to the idle

state and wait for the next operation.

Addressing of the device requires a total of three bytes of information to be sent, representing address bits A23-A0.

Since the upper address limit of the AT25DF081A memory array is 0FFFFFh, address bits A23-A20 are always

ignored by the device.

6 Atmel AT25DF081A

8715B–SFLSH–8/10