AN18207A Просмотр технического описания (PDF) - Panasonic Corporation

Номер в каталоге

Компоненты Описание

производитель

AN18207A Datasheet PDF : 38 Pages

| |||

AN18207A

Technical Data

y I2C-bus interface

1. Basic Rules

x This IC, I2C-bus, is designed to correspond to the Standard-mode (100 kbps) and Fast-mode (400 kbps) devices in the version

2.1 of Philips Co.'s specification. However, it does not correspond to the HS-mode (to 3.4 Mbps).

x This IC will be operated as a slave device in the I2C-bus system.

x The program operation check of this IC has not been conducted on the multi-master bus system and the mix-speed bus system,

yet. The connected confirmation of this IC to the CBUS receiver also has not been checked. Please confirm our company if it

will be used in these mode systems.

x Purchase of Panasonic I2C Components conveys a license under the Philips I2C patent right to use these components in an I2C

systems, provided that the system conforms to the I2C standard specifications as defined by Philips.

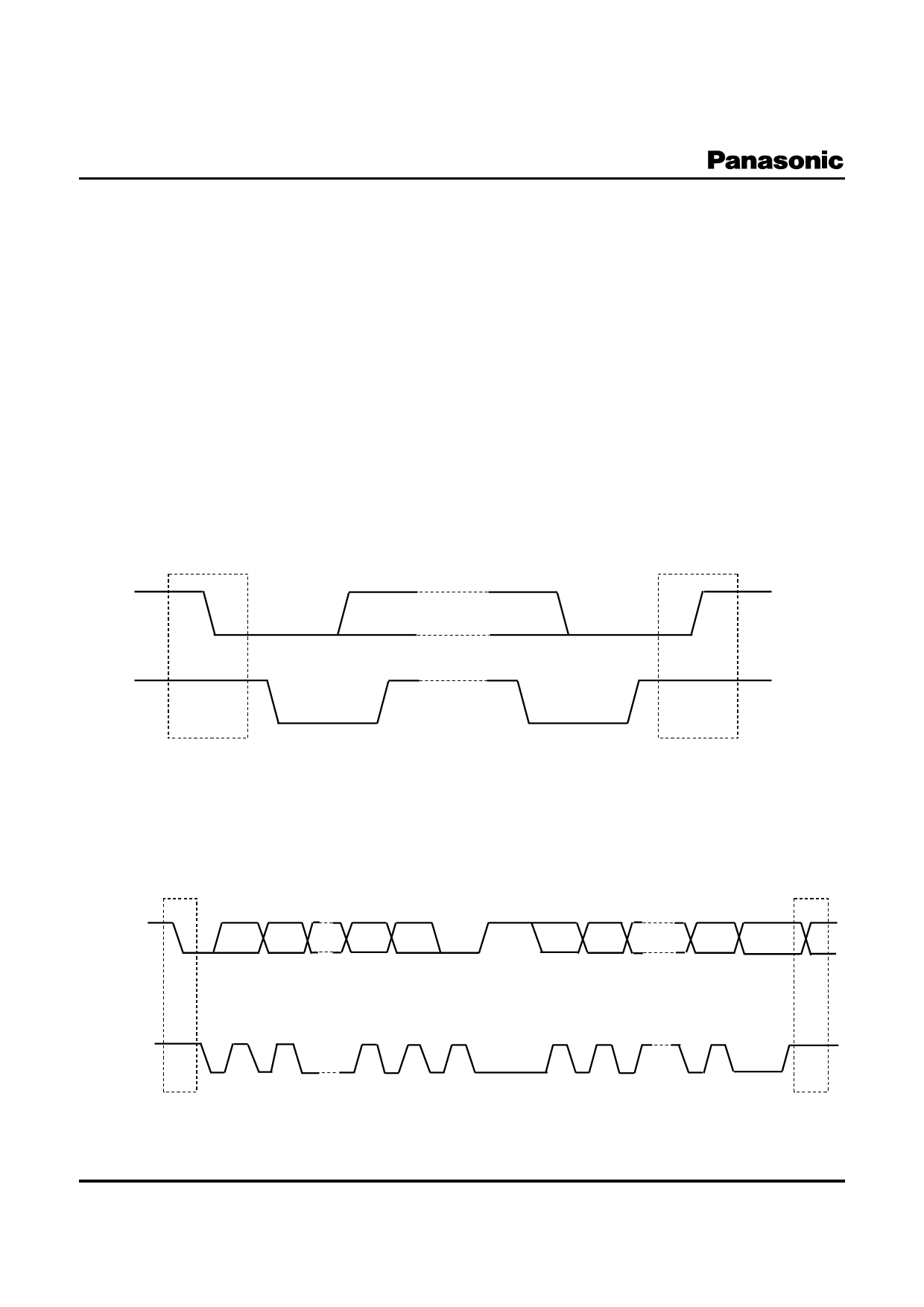

2. START and STOP conditions

A High to Low transition on the SDA line while SCL is High is one such unique case. This situation indicates a START

condition. A Low to High transition on the SDA line while SCL is High defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be free again a certain time after the

STOP condition.

START condition

STOP condition

SDA

SCL

3. Transferring Data

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted.

Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. If a slave can't

receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal

interrupt, it can hold the clock line SCL Low to force the master into a wait state. Data transfer then continues when the slave is

ready for another byte of data and releases clock line SCL.

SDA

MSB

acknowledgement

signal from slave

P

acknowledgement

Sr

signal from receiver

S

SCL

or

1

2

Sr

START or

repeated START

condition

7

89

ACK

SDC00078AEB

Sr

1

2

3–8

9

or

P

ACK

STOP or

repeated START

condition

16