AL700 Просмотр технического описания (PDF) - AverLogic Technologies Inc

Номер в каталоге

Компоненты Описание

производитель

AL700 Datasheet PDF : 82 Pages

| |||

AL700/701/710

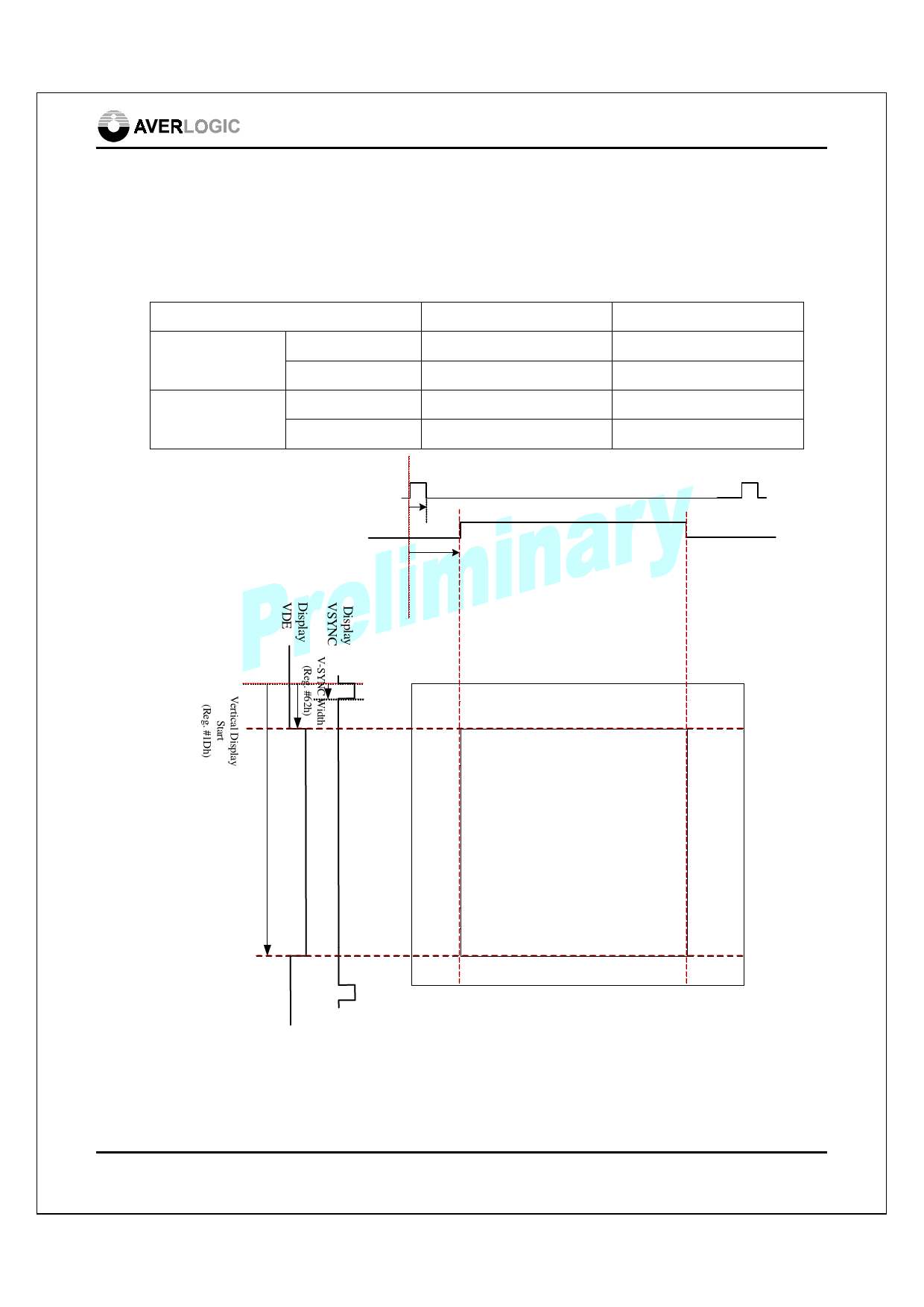

AL700/701/710 uses internal control registers #03h and #04h to adjust output timing with

different sync, flags, data formats and data sequence, and select 8-bit or 16-bit data bus

width. To support various TV encoders, AL700/701/710 uses internal control register #04h

to adjust output timing with different sync, flags, data formats, and data sequence. The

encoder interface can be set to Master or Slave mode by register #18h while using external

encoders. The following table shows the output formats supported by AL700/701/710.

Video System

External encoder

NTSC

PAL

Internal encoder

NTSC

PAL

Total Resolution

858 * 525

864 * 625

910 * 525

1135 * 625

Active Resolution

720 * 480

720 * 576

737 * 480

929 * 576

Display

HSYNC

Display

HDE

H-SYNC Width

(Reg. #61h, #62h)

Horizontal Display

Start

(Reg. #1Bh, 1Ch)

DISPLAY

ACTIVE

REGION

Figure 2: Output Video Timing

The output display system, sync signal pulse width, and active display window are fully

programmable. They are defined by HSYNCWIDTH (#60h, #61h), DISPHSTART (#1Bh,

©2001,2002-Copyright by AverLogic Technologies, Corp. Preliminary Version C1.1 14