ADSP-21991 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADSP-21991 Datasheet PDF : 44 Pages

| |||

ADSP-21991

The encoder interface unit can also be made to implement some

error checking functions. If an encoder count error is detected

(due to a disconnected encoder line, for example), a status bit in

the EIUSTAT register is set, and an EIU count error interrupt is

generated.

The encoder interface unit of the ADSP-21991 contains a 16-bit

loop timer that consists of a timer register, period register and

scale register so that it can be programmed to time out and reload

at appropriate intervals. When this loop timer times out, an EIU

loop timer timeout interrupt is generated. This interrupt could

be used to control the timing of speed and position control loops

in high performance drives.

The encoder interface unit also includes a high performance

encoder event timer (EET) block that permits the accurate timing

of successive events of the encoder inputs. The EET can be pro-

grammed to time the duration between up to 255 encoder pulses

and can be used to enhance velocity estimation, particularly at

low speeds of rotation.

Flag I/O (FIO) Peripheral Unit

The FIO module is a generic parallel I/O interface that supports

sixteen bidirectional multifunction flags or general-purpose

digital I/O signals (PF15–0).

All sixteen FLAG bits can be individually configured as an input

or output based on the content of the direction (DIR) register,

and can also be used as an interrupt source for one of two FIO

interrupts. When configured as input, the input signal can be

programmed to set the FLAG on either a level (level sensitive

input/interrupt) or an edge (edge sensitive input/interrupt).

The FIO module can also be used to generate an asynchronous

unregistered wake-up signal FIO_WAKEUP for DSP core wake

up after power-down.

The FIO Lines, PF7–1 can also be configured as external slave

select outputs for the SPI communications port, while PF0 can

be configured to act as a slave select input.

The FIO Lines can be configured to act as a PWM shutdown

source for the 3-phase PWM generation unit of the

ADSP-21991.

Watchdog Timer

The ADSP-21991 integrates a watchdog timer that can be used

as a protection mechanism against unintentional software events.

It can be used to cause a complete DSP and peripheral reset in

such an event. The watchdog timer consists of a 16-bit timer that

is clocked at the external clock rate (CLKIN or crystal input

frequency).

In order to prevent an unwanted timeout or reset, it is necessary

to periodically write to the watchdog timer register. During

abnormal system operation, the watchdog count will eventually

decrement to 0 and a watchdog timeout will occur. In the system,

the watchdog timeout will cause a full reset of the DSP core and

peripherals.

General-Purpose Timers

The ADSP-21991 contains a general-purpose timer unit that

contains three identical 32-bit timers. The three programmable

interval timers (Timer0, Timer1, and Timer2) generate periodic

interrupts. Each timer can be independently set to operate in one

of three modes:

• Pulse Waveform Generation (PWM_OUT) mode

• Pulsewidth Count/Capture (WDTH_CAP) mode

• External Event Watchdog (EXT_CLK) mode

Each Timer has one bidirectional chip pin, TMR2-0. For each

timer, the associated pin is configured as an output pin in

PWM_OUT Mode and as an input pin in WDTH_CAP and

EXT_CLK Modes.

Interrupts

The interrupt controller lets the DSP respond to 17 interrupts

with minimum overhead. The DSP core implements an interrupt

priority scheme as shown in Table 2. Applications can use the

unassigned slots for software and peripheral interrupts. The

Peripheral Interrupt Controller is used to assign the various

peripheral interrupts to the 12 user assignable interrupts of the

DSP core.

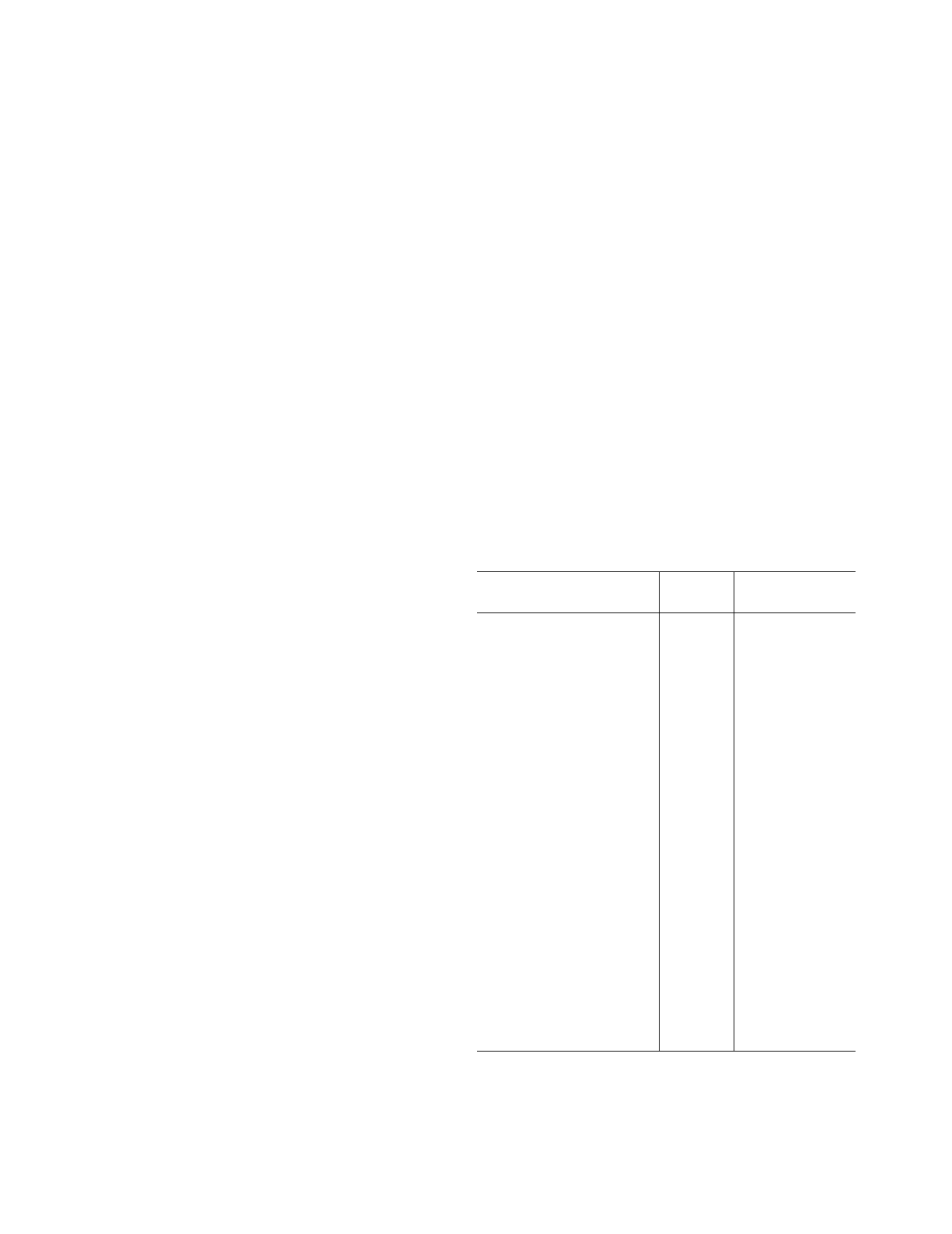

Table 2. Interrupt Priorities/Addresses

Interrupt

Emulator (NMI)

—Highest Priority

Reset (NMI)

Power-Down (NMI)

Loop and PC Stack

Emulation Kernel

User Assigned Interrupt

(USR0)

User Assigned Interrupt

(USR1)

User Assigned Interrupt

(USR2)

User Assigned Interrupt

(USR3)

User Assigned Interrupt

(USR4)

User Assigned Interrupt

(USR5)

User Assigned Interrupt

(USR6)

User Assigned Interrupt

(USR7)

User Assigned Interrupt

(USR8)

IMASK/

IRPTL

NA

Vector Address

NA

0

0x00 0000

1

0x00 0020

2

0x00 0040

3

0x00 0060

4

0x00 0080

5

0x00 00A0

6

0x00 00C0

7

0x00 00E0

8

0x00 0100

9

0x00 0120

10

0x00 0140

11

0x00 0160

12

0x00 0180

–10–

REV. 0