ADSP-2196MKCA-160X Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADSP-2196MKCA-160X Datasheet PDF : 68 Pages

| |||

35(/,0,1$5< 7(&+1,&$/ '$7$

September 2001 For current information contact Analog Devices at 800/262-5643

ADSP-2196

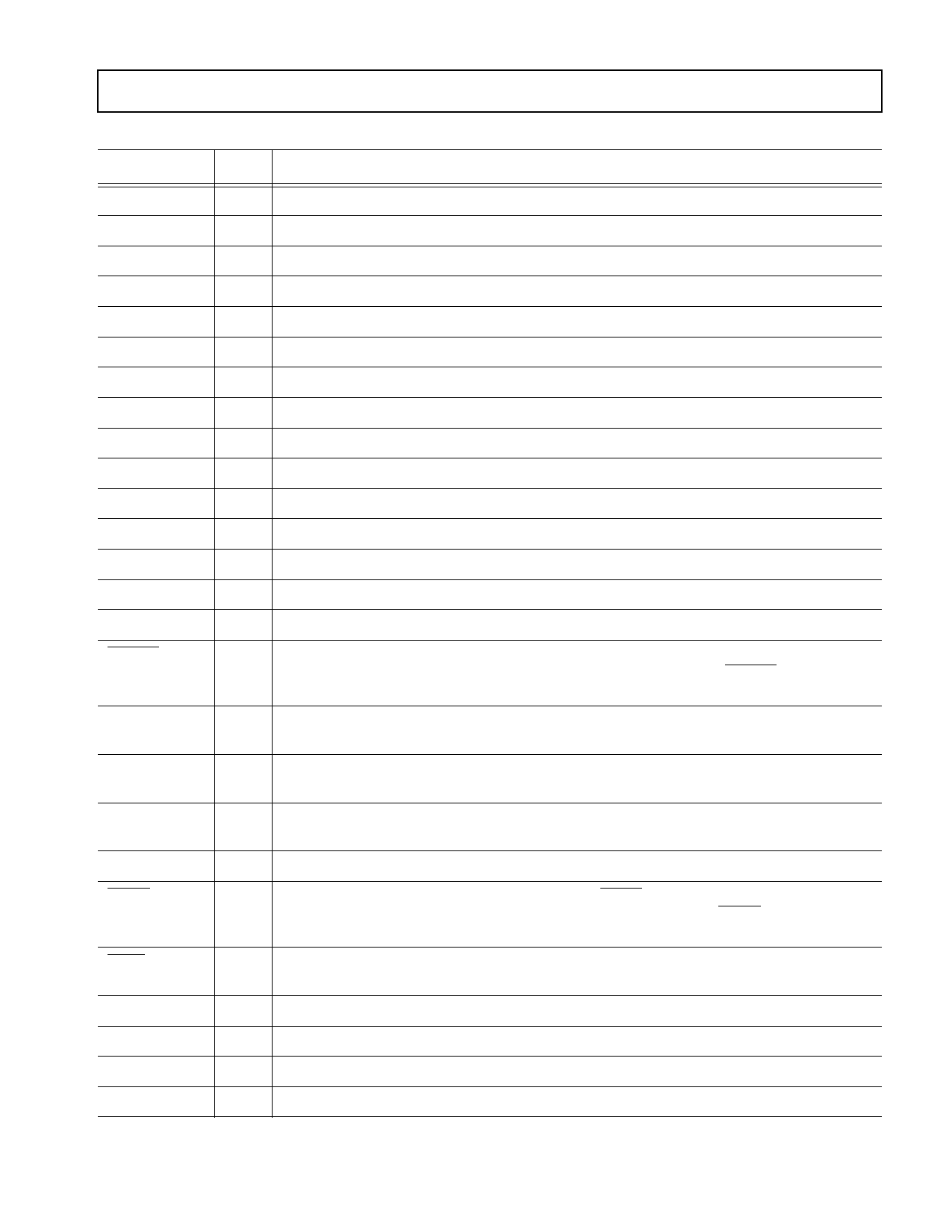

Table 7. Pin Descriptions (Continued)

Pin

Type Function

RCLK1–0

I/O/T SPORT1–0 Receive Clock

RCLK2/SCK1 I/O/T SPORT2 Receive Clock/SPI1 Serial Clock

RFS1–0

I/O/T SPORT1–0 Receive Frame Sync

RFS2/MOSI1 I/O/T SPORT2 Receive Frame Sync/SPI1 Master-Output, Slave-Input data

TCLK1–0

I/O/T SPORT1–0 Transmit Clock

TCLK2/SCK0 I/O/T SPORT2 Transmit Clock/SPI0 Serial Clock

TFS1–0

I/O/T SPORT1–0 Transmit Frame Sync

TFS2/MOSI0 I/O/T SPORT2 Transmit Frame Sync/SPI0 Master-Output, Slave-Input data

DR1–0

I/T SPORT1–0 Serial Data Receive

DR2/MISO1 I/O/T SPORT2 Serial Data Receive/SPI1 Master-Input, Slave-Output data

DT1–0

O/T SPORT1–0 Serial Data Transmit

DT2/MISO0 I/O/T SPORT2 Serial Data Transmit/SPI0 Master-Input, Slave-Output data

TMR2–0

I/O/T Timer output or capture

RXD

I

UART Serial Receive Data

TXD

O

UART Serial Transmit Data

RESET

TCK

I

Processor Reset. Resets the ADSP-2196 to a known state and begins execution at the program

memory location specified by the hardware reset vector address. The RESET input must be

asserted (low) at power-up. The RESET pin has a 85 kΩ internal pull-up resistor.

I

Test Clock (JTAG). Provides a clock for JTAG boundary scan. The TCK pin has a 85 kΩ

internal pull-up resistor.

TMS

I

Test Mode Select (JTAG). Used to control the test state machine. The TMS pin has a 85 kΩ

internal pull-up resistor.

TDI

TDO

I

Test Data Input (JTAG). Provides serial data for the boundary scan logic. The TDI pin has

a 85 kΩ internal pull-up resistor.

O

Test Data Output (JTAG). Serial scan output of the boundary scan path.

TRST

I

Test Reset (JTAG). Resets the test state machine. TRST must be asserted (pulsed low) after

power-up or held low for proper operation of the ADSP-2196. The TRST pin has a 65 kΩ

internal pull-down resistor.

EMU

O

Emulation Status (JTAG). Must be connected to the ADSP-2196 emulator target board

connector only.

VDDINT

VDDEXT

GND

P

Core Power Supply. Nominally 2.5 V dc and supplies the DSP’s core processor. (four pins).

P

I/O Power Supply; Nominally 3.3 V dc. (nine pins).

G

Power Supply Return. (twelve pins).

NC

Do Not Connect. Reserved pins that must be left open and unconnected.

REV. PrA

This information applies to a product under development. Its characteristics and specifications are subject to change with-

21

out notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.