ADSP-2192M Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADSP-2192M Datasheet PDF : 40 Pages

| |||

ADSP-2192M

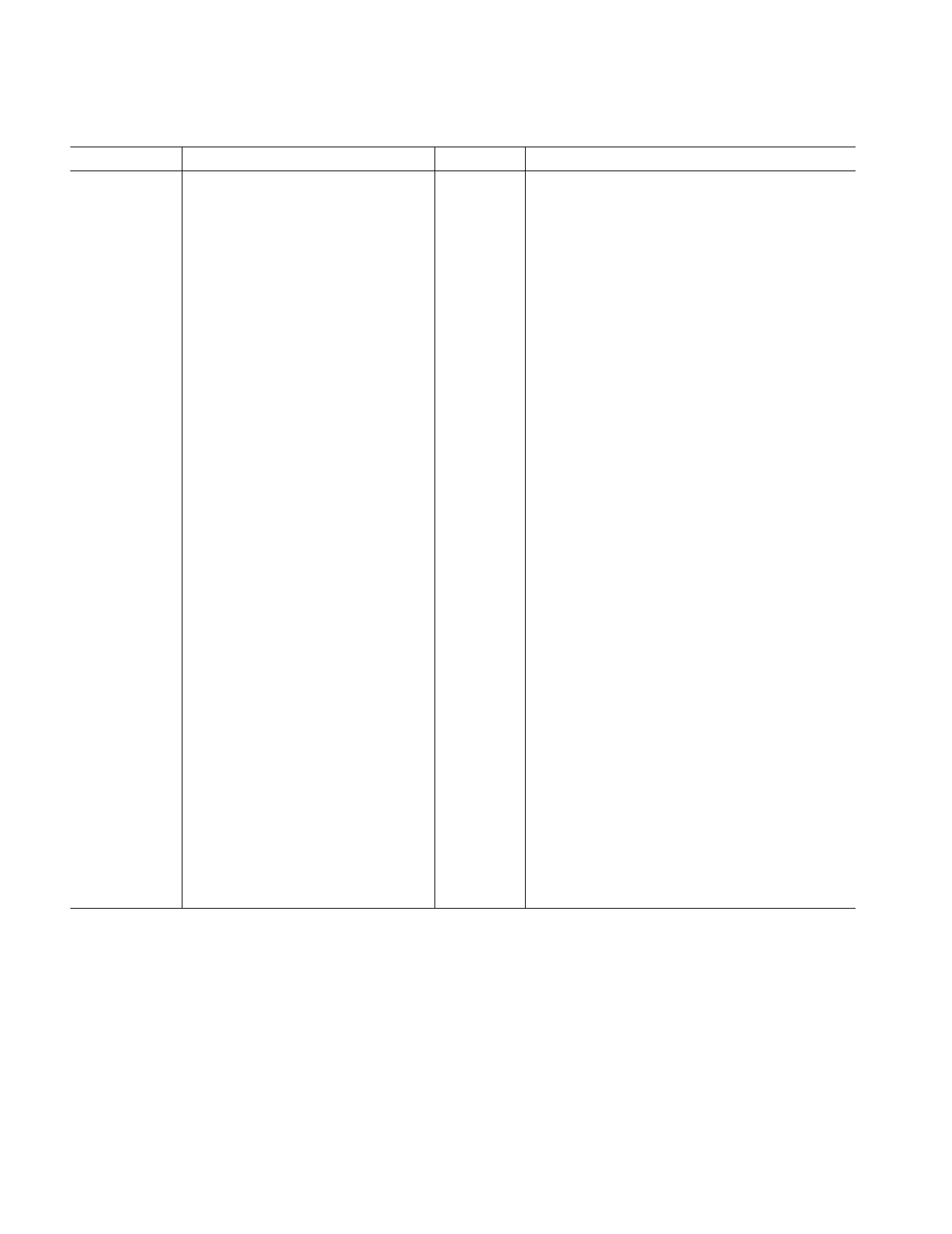

Table 7. PCI Configuration Space 0, 1, and 2

Address

0x01–0x00

0x03–0x02

0x05–0x04

Name

Vendor ID

Config 0 Device ID

Config 1 Device ID

Config 2 Device ID

Command Register

Reset

0x11D4

0x2192

0x219A

0x219E

0x0

0x07–0x06

Status Register

0x0

0x08

0x0B–0x09

0x0C

0x0D

0x0E

0x0F

0x13–0x10

Revision ID

Class Code

Cache Line Size

Latency Timer

Header Type

BIST

Base Address 1

0x0

0x48000

0x0

0x0

0x80

0x0

0x08

0x17–0x14

0x1B–0x18

0x1F–0x1C

0x23–0x20

0x27–0x24

0x2B–0x28

0x2D–0x2C

0x2F–0x2E

0x33–0x30

0x34

0x3C

0x3D

0x3E

0x3F

0x40

0x41

0x43–0x42

0x45–0x44

0x46

0x47

Base Address2

Base Address3

Base Address4

Base Address5

Base Address6

Config 0 CardBus CIS Pointer

Config 1 CardBus CIS Pointer

Config 2 CardBus CIS Pointer

Subsystem Vendor ID

Config 0 Subsystem Device ID

Config 1 Subsystem Device ID

Config 2 Subsystem Device ID

Expansion ROM Base Address

Capabilities Pointer

Interrupt Line

Interrupt Pin

Min_Gnt

Max_Lat

Capability ID

Next_Cap_Ptr

Power Management Capabilities

Power Management Control/Status

Power Management Bridge

Power Management Data

0x08

0x08

0x01

0x0

0x0

0x1FF03

0x1FE03

0x1FD03

0x11D4

0x2192

0x219A

0x219E

0x0

0x40

0x0

0x1

0x1

0x4

0x1

0x0

0x6C22

0x0

0x0

0x0

Comments

Writable from the DSP during initialization

Writable from the DSP during initialization

Writable from the DSP during initialization

Writable from the DSP during initialization

Bus Master, Memory Space Capable, I/O Space

Capable

Bits enabled: Capabilities List, Fast B2B,

Medium Decode

Writable from the DSP during initialization

Writable from the DSP during initialization

Read Only

Multifunction bit set

Unimplemented

Register Access for all ADSP-2192M Registers,

Prefetchable Memory

24-bit DSP Memory Access

16-bit DSP Memory Access

I/O access for control registers and DSP memory

Unimplemented

Unimplemented

CIS RAM Pointer - Function 0 (Read Only)

CIS RAM Pointer - Function 1 (Read Only)

CIS RAM Pointer - Function 2 (Read Only)

Writable from the DSP during initialization

Writable from the DSP during initialization

Writable from the DSP during initialization

Writable from the DSP during initialization

Unimplemented

Read Only

Uses INTA Pin

Read Only

Read Only

Power Management Capability Identifier

Read Only

Writable from the DSP during initialization

Bits 15 and 8 initialized only on Power-up

Unimplemented

Unimplemented

PCI Memory Map

The ADSP-2192M On-Chip Memory is mapped to the PCI

Address Space. Because some ADSP-2192M Memory Blocks

are 24 bits wide (Program Memory) while others are 16 bits

(Data Memory), two different footprints are available in PCI

Address Space. These footprints are available to each PCI

function by accessing different PCI Base Address Registers

(BAR). BAR2 supports 24-bit “Unpacked” Memory Access.

BAR3 supports 16-bit “Packed” Memory Access.

In 24-bit (BAR2) Mode, each 32 bits (four Consecutive PCI

Byte Address Locations, which make up one PCI Data word)

correspond to a single ADSP-2192M Memory Location. BAR2

Mode is typically used for Program Memory Access. Byte3 is

always unused. Bytes[2:0] are used for 24-bit Memory Locations.

As shown in Figure 3, Bytes[2:1] are used for 16-bit Memory

Locations.

In 16-bit (BAR3) Mode (Figure 4), each 32-bit (four Consecu-

tive PCI Byte Address Locations) PCI Data Word corresponds

to two ADSP-2192M Memory Locations. Bytes[3:2] contain

one 16-bit Data Word, Bytes[1:0] contain a second 16-bit Data

Word. BAR3 Mode is typically used for Data Memory Access.

Only the 16 MSBs of a Data Word are accessed in 24-bit Blocks;

the 8 LSBs are ignored.

–10–

REV. 0