ADSP-2191M Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADSP-2191M Datasheet PDF : 52 Pages

| |||

ADSP-2191M

assigned a priority level of 11 are aliased to the lowest priority bit

position (15) in these registers and share vector address

0x00 01E0.

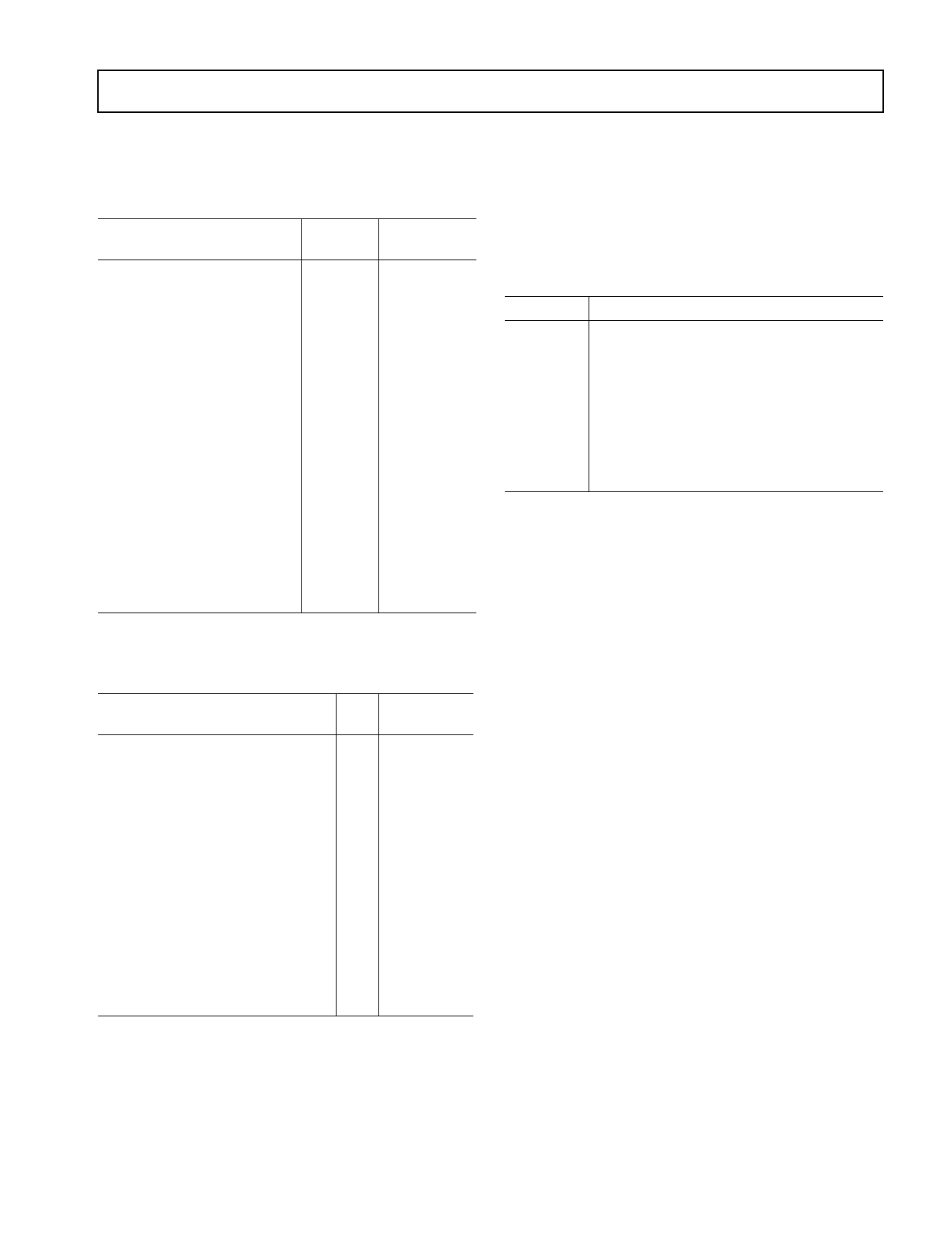

Table 1. Interrupt Priorities/Addresses

Interrupt

IMASK/ Vector

IRPTL Address1

Emulator (NMI)—

NA

Highest Priority

Reset (NMI)

0

Power-Down (NMI)

1

Loop and PC Stack

2

Emulation Kernel

3

User Assigned Interrupt

4

User Assigned Interrupt

5

User Assigned Interrupt

6

User Assigned Interrupt

7

User Assigned Interrupt

8

User Assigned Interrupt

9

User Assigned Interrupt

10

User Assigned Interrupt

11

User Assigned Interrupt

12

User Assigned Interrupt

13

User Assigned Interrupt

14

User Assigned Interrupt— 15

Lowest Priority

NA

0x00 0000

0x00 0020

0x00 0040

0x00 0060

0x00 0080

0x00 00A0

0x00 00C0

0x00 00E0

0x00 0100

0x00 0120

0x00 0140

0x00 0160

0x00 0180

0x00 01A0

0x00 01C0

0x00 01E0

1These interrupt vectors start at address 0x10000 when the DSP is in

“no-boot,” run from external memory mode.

Table 2. Peripheral Interrupts and Priority at Reset

Interrupt

Reset

ID Priority

Slave DMA/Host Port Interface 0 0

SPORT0 Receive

11

SPORT0 Transmit

22

SPORT1 Receive

33

SPORT1 Transmit

44

SPORT2 Receive/SPI0

55

SPORT2 Transmit/SPI1

66

UART Receive

77

UART Transmit

88

Timer 0

99

Timer 1

10 10

Timer 2

11 11

Programmable Flag A (any PFx) 12 11

Programmable Flag B (any PFx) 13 11

Memory DMA port

14 11

Interrupt routines can either be nested with higher priority inter-

rupts taking precedence or processed sequentially. Interrupts can

be masked or unmasked with the IMASK register. Individual

interrupt requests are logically ANDed with the bits in IMASK;

the highest priority unmasked interrupt is then selected. The

emulation, power-down, and reset interrupts are nonmaskable

with the IMASK register, but software can use the DIS INT

instruction to mask the power-down interrupt.

The Interrupt Control (ICNTL) register controls interrupt

nesting and enables or disables interrupts globally.

The general-purpose Programmable Flag (PFx) pins can be con-

figured as outputs, can implement software interrupts, and (as

inputs) can implement hardware interrupts. Programmable Flag

pin interrupts can be configured for level-sensitive, single

edge-sensitive, or dual edge-sensitive operation.

Table 3. Interrupt Control (ICNTL) Register Bits

Bit

0–3

4

5

6

7

8–9

10

11

12–15

Description

Reserved

Interrupt Nesting Enable

Global Interrupt Enable

Reserved

MAC-Biased Rounding Enable

Reserved

PC Stack Interrupt Enable

Loop Stack Interrupt Enable

Reserved

The IRPTL register is used to force and clear interrupts. On-chip

stacks preserve the processor status and are automatically main-

tained during interrupt handling. To support interrupt, loop, and

subroutine nesting, the PC stack is 33 levels deep, the loop stack

is eight levels deep, and the status stack is 16 levels deep. To

prevent stack overflow, the PC stack can generate a stack-level

interrupt if the PC stack falls below three locations full or rises

above 28 locations full.

The following instructions globally enable or disable interrupt

servicing, regardless of the state of IMASK.

ENA INT;

DIS INT;

At reset, interrupt servicing is disabled.

For quick servicing of interrupts, a secondary set of DAG and

computational registers exist. Switching between the primary

and secondary registers lets programs quickly service interrupts,

while preserving the DSP’s state.

DMA Controller

The ADSP-2191M has a DMA controller that supports

automated data transfers with minimal overhead for the DSP

core. Cycle stealing DMA transfers can occur between the

ADSP-2191M’s internal memory and any of its DMA-capable

peripherals. Additionally, DMA transfers can be accomplished

between any of the DMA-capable peripherals and external

devices connected to the external memory interface. DMA-capa-

ble peripherals include the Host port, SPORTs, SPI ports, and

UART. Each individual DMA-capable peripheral has a dedicated

DMA channel. To describe each DMA sequence, the DMA con-

troller uses a set of parameters—called a DMA descriptor. When

successive DMA sequences are needed, these DMA descriptors

can be linked or chained together, so the completion of one DMA

sequence auto-initiates and starts the next sequence. DMA

sequences do not contend for bus access with the DSP core;

instead DMAs “steal” cycles to access memory.

REV. 0

–7–