AD9826 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD9826 Datasheet PDF : 20 Pages

| |||

AD9826

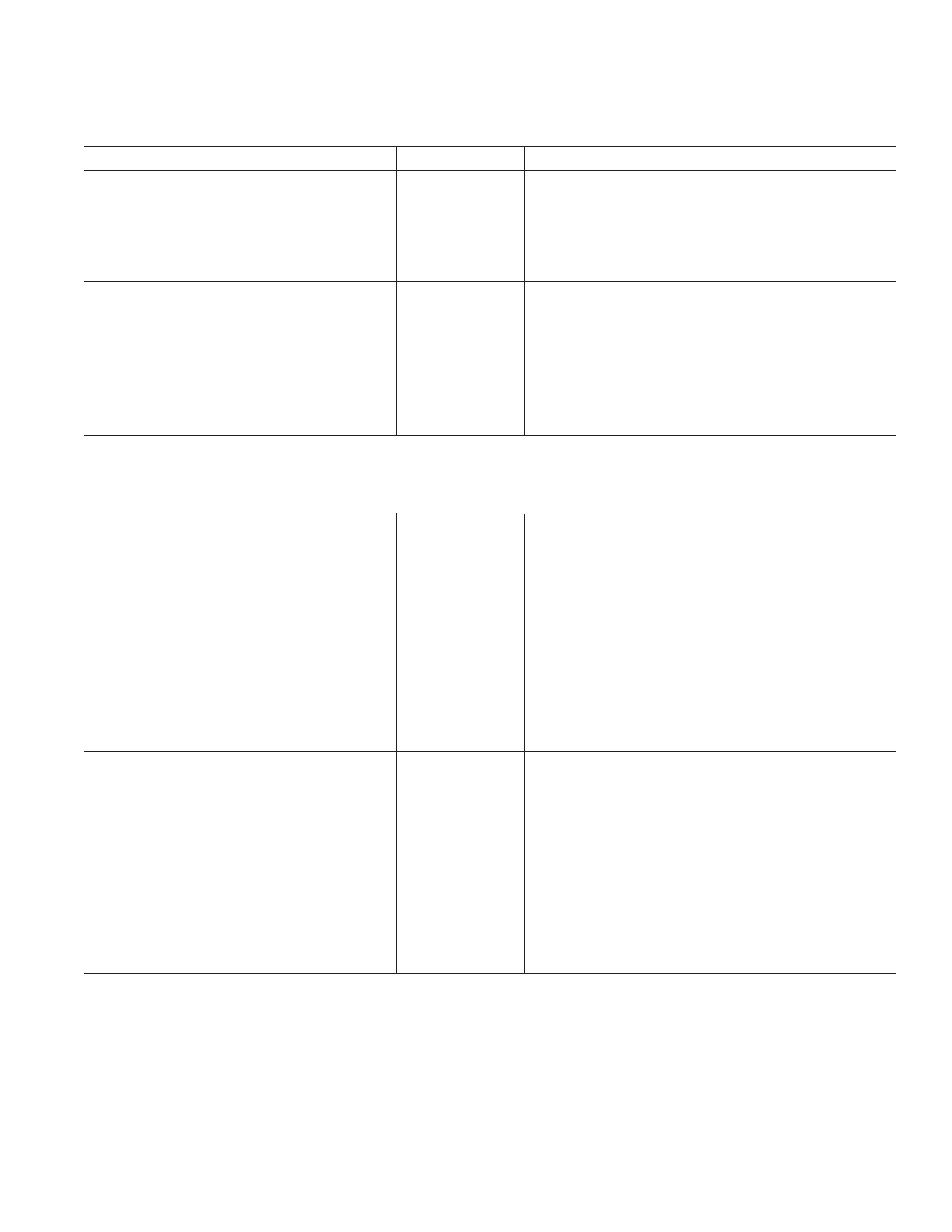

DIGITAL SPECIFICATIONS (TMIN to TMAX, AVDD = 5 V, DRVDD = 5 V, CDS Mode, fADCCLK = 15 MHz, fCDSCLK1 = fCDSCLK2 = 5 MHz,

CL = 10 pF, unless otherwise noted.)

Parameter

LOGIC INPUTS

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

Input Capacitance

LOGIC OUTPUTS

High Level Output Voltage

Low Level Output Voltage

High Level Output Current

Low Level Output Current

LOGIC OUTPUTS (with DRVDD = 3 V)

High Level Output Voltage, (IOH = 50 μA)

Low Level Output Voltage (IOL = 50 μA)

Specifications subject to change without notice.

Symbol

VIH

VIL

IIH

IIL

CIN

VOH

VOL

IOH

IOL

VOH

VOL

Min

Typ

Max

Unit

2.0

10

10

10

V

0.8

V

μA

μA

pF

4.5

50

50

V

0.1

V

μA

μA

2.95

V

0.05

V

TIMING SPECIFICATIONS (TMIN to TMAX, AVDD = 5 V, DRVDD = 5 V, specs are for 16-bit performance.)

Parameter

Symbol

Min

CLOCK PARAMETERS

3-Channel Pixel Rate

tPRA

200

1-Channel Pixel Rate

tPRB

80

ADCCLK Pulsewidth

tADCLK

30

CDSCLK1 Pulsewidth

tC1

8

CDSCLK2 Pulsewidth

tC2

8

CDSCLK1 Falling to CDSCLK2 Rising

tC1C2

0

ADCCLK Falling to CDSCLK2 Rising

tADC2

0

CDSCLK2 Rising to ADCCLK Rising

tC2ADR

5

CDSCLK2 Falling to ADCCLK Falling

tC2ADF

30

CDSCLK2 Falling to CDSCLK1 Rising

tC2C1

5

Aperture Delay for CDS Clocks

tAD

SERIAL INTERFACE

Maximum SCLK Frequency

fSCLK

10

SLOAD to SCLK Set-Up Time

tLS

10

SCLK to SLOAD Hold Time

tLH

10

SDATA to SCLK Rising Set-Up Time

tDS

10

SCLK Rising to SDATA Hold Time

tDH

10

SCLK Falling to SDATA Valid

tRDV

10

DATA OUTPUTS

Output Delay

tOD

3-State to Data Valid

tDV

Output Enable High to 3-State

tHZ

Latency (Pipeline Delay)

NOTES

It is recommended that CDSCLK falling edges do not occur within the first 10 ns following an ADCCLK edge.

Specifications subject to change without notice.

Typ

2

6

10

10

3 (Fixed)

Max

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

ns

ns

ns

ns

ns

ns

ns

ns

Cycles

REV. B

–3–